## A CONTROLLER COMPUTER INTERFACE AND DRIVER FOR A RADIO TELESCOPE

Bachelor of Engineering in ELECTRONICS & COMMUNICATION

by

VIHAR. R. RAI ROQUE NELSON PINTO GIRISH KRISHNAN

### DEPARTMENT OF ELECTRONICS & COMMUNICATION BANGALORE INSTITUTE OF TECHNOLOGY

K. R. ROAD

**BANGALORE - 560 004**

1990 - 91

### RAMAN RESEARCH INSTITUTE BANGALORE-560 080 INDIA

#### CERTIFICATE

THIS IS TO CERTIFY THAT THE FOLLOWING STUDENTS HAVE SATISFACTORILY COMPLETED THE PROJECT ENTITLED:

A CONTROLLER COMPUTER INTERFACE AND DRIVER FOR A RADIO TELESCOPE SYSTEM "

CARRIED OUT AT RAMAN RESEARCH INSTITUTE IN PARTIAL FULFILMENT OF THE AWARD OF "BACHELOR'S DEGREE IN ELECTRONICS AND COMMUNICATION ENGINEERING "FOR THE BANGALORE UNIVERSITY DURING THE YEAR 1990 - 91

VIHAR R. RAI ROQUE NELSON PINTO GIRISH KRISHNAN

N. udayo har

DR N. UDAYA <sup>I</sup>SHANKAR SCIENTIST RAMAN RESEARCH INSTITUTE C.V. RAMAN AVENUE BANGALORE 560 080 BANGALORE INSTITUTE OF TECHNOLOGY

#### CERTIFICATE

#### THIS IS TO CERTIFY THAT THE PROJECT ENTITLED:

A CONTROLLER COMPUTER INTERFACE AND DRIVER FOR A RADIO TELESCOPE SYSTEM "

SUBMITTED BY

VIHAR R. RAI ROQUE NELSON PINTO GIRISH KRISHNAN

IN PARTIAL FULFILMENT OF THE REQUIREMENTS OF THE AWARD OF BACHELOR'S DEGREE IN ELECTRONICS ENGINEERING

FROM BANGALORE INSTITUTE OF TECHNOLOGY FOR THE BANGALORE UNIVERSITY DURING THE YEAR 1990 - 91, IS A RECORD OF BONAFIDE WORK CARRIED OUT BY THEM IN RAMAN RESEARCH INSTITUTE BANGALORE.

B. NARAYANAPPA PROF.

HEAD OF DEPARTMENT ELECTRONICS & COMMUNICATION B I T BANGALORE

end d.

MR. SATYA PRASAD LANKA LECTURER ELECTRONICS & COMMUNICATION B I T BANGALORE

#### ACKNOWLEDGEMENT

Firstly, we express our gratitude to Prof. B.Narayanappa, Head of Department Electronics and Communication for giving us permission to conduct our project at Raman Research Institute.

We are also grateful to our guides Mr. N.Jayaprakash and Dr. N Udayashankar as well as Mr Satyaprakash Lanka of BIT for offering us their unstinting encouragment and guidance through out the course of this project.

Thanks are also due to them for guiding us out of those abundant and intractable 'dead ends' we encountered in the course of understanding the system and when designing the proposed system.

Our special salutations to "J.P." for his remarkable patience....

Our sincere thanks to Arvind Shenoy, Umesh Nayak, Shivkumar Nair, Rajiv Agarwal and B. Atmaram who always made themselves available for discussions and comments.

We wish to thank our classmate Ikram Khan whose suggestions on microprocessor design we found indispensable. Thanks are also due to John Aranha and Gerard Da Costa.

We also thank in general all those lecturers who impeccably

taught us through our years in college. Without the grounding their lectures provided, we would not have been able to attempt this project.

Vihar R.Rai Roque Nelson Pinto Girish Krishnan

#### CONTENTS

- \* SYNOPSIS

- \* INTRODUCTION

- \* THE EXISTING SYSTEM

- \* THE PROPOSED SYSTEM

- \* DATA SHEETS

- \* BIBLIOGRAPHY

## SYNOPSIS

BIT - DEPT OF ELECTRONICS AND COMMUNICATION 1990 - 1991

#### A CONTROLLER

COMPUTER INTERFACE AND DRIVER FOR A RADIO TELESCOPE CORRELATOR SYSTEM

#### A SYNOPSIS

#### INTRODUCTION

Radio Telescope is used to study the radiation from celestial objects in space, in the Radio frequency region. ( Roughly in millimeter to meter long waves )

A Radio Telescope in its simplest form consists of three elements.

a) Antenna:

The antenna collects electromagnetic radiation from a selected region of the sky.

b) Receiver:

The output of the antenna is fed to the input of a receiver. A receiver amplifies a certain specified band of frequency and conditions it for further processing. In the simplest configuration the output of the receiver is fed to a detector

whose output is proportional to the power of the input radiations.

c) Indicator:

The indicator registers the detector reading and records it.

#### INTERFEROMETRY

A Radio Interferometer has two antennas separated by a distance and has their outputs multiplied in a correlator.

It is designed to give an output proportional to the average product of the voltages from the two antennas. In an interferometer the signal from the celestial source reaches the two elements with a small time difference. The delay is removed by a delay unit and then correlated to give a measure of one of the fourier components of the ratio brightness distribution.

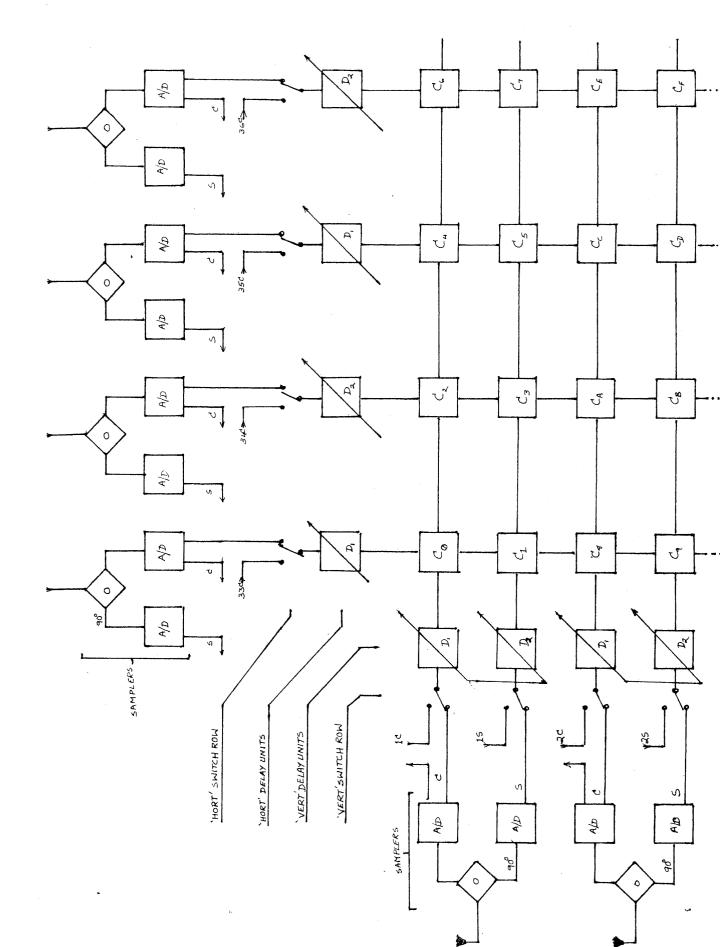

A digital correlator system employs samplers each compromising of an orthogonal power splitter and two A/D converters. ( one for each component ) The sampler outputs are input to the delay units to suitably delay the signals. Then they are correlated in the correlators which is nothing but a process of multiplication and integration carried out in a multiplier and an accumulator.

This project describes the design of a 1024 channel B I T - Dept of Electronics and Communication 1990 - 91 correlation receiver interface to a computer. The computer by an extensive decoding process selects and reads all the correlator outputs in a sequence via the interface.

DATA COLLECTOR

The computer interface serves the purpose of collecting and holding the correlator output data for the computer to read.

CONTROLLER - COMPUTER INTERFACE AND DRIVER OR MASTER CONTROLLER

It also enables the computer to output control signals to the correlator and delay circuits ( and samplers ).

A list of input to the master control board and their corresponding outputs are as follows.

Inputs : modify / reset code

Outputs : a) active resets

- b) interrupt signals

- c) reset signals

- d) integration bank select signals

- Inputs

- : A 48 MHz basic oscillator signal

Outputs : a) a four phase clock

b) a 5.46 ms timing pattern

- c) update signals

- d) blanking signals

# INTRODUCTION

BIT - DEPT OF ELECTRONICS AND COMMUNICATION 1990 - 1991

#### INTRODUCTION

Radio Telescope is used to study the radiation from celestial objects in space, in the Radio frequency region. ( Roughy millimeter to meter long waves )

In 1932 a Bell Laboratories engineer, Karl Jansky, was investigating radio reception of an antenna system in order to design a Trans Atlantic telephone system. His antenna, about 100 feet long and pivoted so that the whole contraption could rotate, pinpointed a mysterious source of radiation. Surprisingly the radiation came from no where on earth, but from the centre of our galaxy, some 30,000 light years away. His study was much later continued by Grote Reber who on studing Jansky's report built his own Radio Telescope and studied the galactic nucleus, which hidden by a gas cloud could not be studied by optical means. Reber pinpointed some strong sources. Ever since Radio Telescope has contributed a lot to the progress in astronomy.

A Radio Telescope in its simplest form consists of three elements.

a) Antenna:

The antenna collects electromagnetic radiation from a selected region of the sky.

b) Receiver:

The output of the antenna is fed to the input of a

receiver. A receiver amplifies a certain specified band of frequency and conditions it for further processing. In the simplest configuration the output of the receiver is fed to a detector whose output is proportional to the power of the input radiation.

c) Indicator:

The indicator registers the detector reading and records it.

#### ANTENNAS

Radio waves from celestial objects are very weak and therefore the aperture of a radio telescope should be sufficiently large to get a clear image. A single telescope of very large aperture would be physically impractical to construct. Therefore radio telescopes of large apertures are built by using extended arrays of smaller telescopes which together make up a large aperture and are easily steerable.

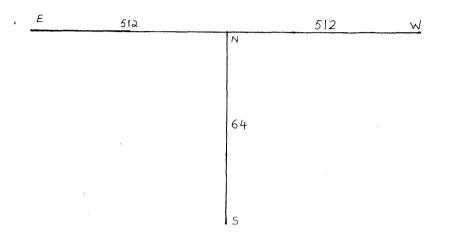

The controller described in the present project was designed for a 1024 channel correlator system. This in turn is a receiver system for an array of helical antennas arranged in the form of a 'T'. The EW (east west) arm is two kilometres long and has 1024 antennas. The NS (north south) arm has 16 rows of 4 antennas each on movable trolleys. Before being fed into the samplers the outputs of every four antennas are combined in a four way power combiner. The outputs of eight such adjacent

combiners in the EW array are further combined in an eight way power combiner. The 48 group outputs after suitable amplification in the field are brought to a central receiver room. 32 outputs from EW array and 16 from NS array are further processed in a 16 X 32 = 512 channel complex correlation receiver.

These antenna outputs are passband signals and are mathematically to be regarded as vector signals containing both amplitude and phase information. The signals are split into two orthogonal signals by a phase splitter. In a complex correlator the signals are split into two orthogonal signals by a quadrature phase splitter Each sub matrix of  $4 \times 4 = 16$  correlators form a correlator unit and are controlled by one microprocessor.

Inspite of carefully shielding the RF line-receivers and IF lines there is always a certain amount of cross talk between the individual channels. This causes spurious correlation over long integration intervals. To reduce Cross Talk a concept called Walsh Switching is used.

The Walsh function generator uses the same clock period as 16 the system. ( 2 / 12 micro seconds = 5.56 ms )

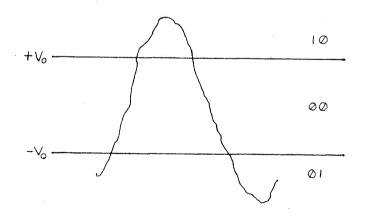

SAMPLER UNITS

The sampler units split analogue input signals into an in phase and a quadrature phase signal and then performs, in both paths, a two bit three level A/D conversion at a clock rate of 12 MHz. The analogue signal is compared with two levels, a +Vo and a -Vo, and a two bit code is generated which indicates if the analogue signal is above the upper level ( +Vo ), below the lower level ( -Vo ) or betweem them.

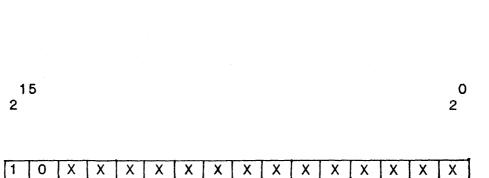

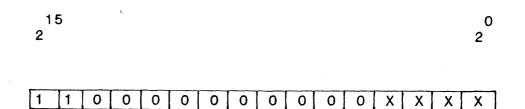

A/D Conversion in the Sampler

ŧ

| *<br>X | x | x  |

|--------|---|----|

| 1      | 0 | +1 |

| 0      | 0 | 0  |

| 0      | 1 | -1 |

DELAY UNITS

The delay lines delay the two input bits X and X for the programmed number of clock intervals. The first phase switch is located at the delay line inputs and is used to synchronously demodulate the corresponding switch on the analogue end. It is called PS Walsh as the switch function will be a Walsh function. The second phase switch is located at one end of the two outputs of the delay line. It represents the synchronous modulation which is needed to get rid of the offset, in the correlators, provided for unidirectional counting.

The delays are individually programmable using the delay programming code.

Delay settings are stored on the delay line boards. All the delay line inputs are connected in parallel to the computer outputs. The same decoder is used to clock a delay setting into

a specific delay line and to enable correlator outputs.

#### CORRELATORS

The correlators multiply outputs of the delay lines and integrate them over a certain period of time.

Two custom made chips VLA 1 and VLA2 constitute the heart of the correlators and are designed to perform two bit three level correlation.

The VLA 1 performs the multiplication and VLA 2 the addition.

| Actual signal level    | Symbolic notation | + bit | - bit |

|------------------------|-------------------|-------|-------|

| Signal > +Vref         | +1                | 1     | 0     |

| -Vref < Signal < +Vref | 0                 | 0     | 0     |

| Signal < -Vref         | -1                | 0     | 1     |

The VLA 1 contain basically a multiplication logic and the VLA 2 is a 14 bit unidirectional counter.

Three level approach was chosen for it gives a good compromise between complexity of hardware and signal to noise ratio.

An appropriate multiplication table for the purpose is shown.

| Xa | Xb |   |    |  |

|----|----|---|----|--|

|    | +1 | 0 | -1 |  |

| +1 | +1 | 0 | -1 |  |

| 0  | 0  | 0 | 0  |  |

| -1 | -1 | 0 | +1 |  |

In the present correlator system the multiplication table is modified according to the table below.

| ( Xa )            |                | (Xb)           |                |

|-------------------|----------------|----------------|----------------|

|                   | +1 (10)        | 0 (00)         | -1 (01)        |

|                   |                |                |                |

| +1 (10)<br>0 (00) | add 2<br>add 1 | add 1<br>add 1 | add 0<br>add 1 |

| -1 (01)           | add 0          | add 1          | add 1          |

| , (01)            |                | auui           | auu z          |

The modification in the table is seen to be the addition of an offset of 1 to every product. The reason for this is that the VLA 2 consists of unidirectional counters only. The offset thus allows the counter to count up only and not down, which would be

necessary if there were to be a -1 output. However for correct integration, the data should be stripped of this offset before the computer reads it. This is done by using a concept called Phase switching, where data bits from the 'vert' delay outputs are periodically inverted and a corresponding inversion occurs to the data at the correlator outputs. One phase switch is included at one of the two delay line outputs. Another is present at the correlator output. An inversion at the delay line output is accompanied by an inversion in the microprocessors sign bit. When it accumulates the correlator outputs. The offset thus gets counted up in one switch interval and down in the other while only the information gets accumulated.

#### CENTRAL OUTPUT COLLECTOR

The central output collector interfaces the correlator output to the computer. The computer selects and reads all the correlators in sequence through the data collector. It serves the purpose of collecting and holding the correlator output data for the computer to read.

In an integration interval the correlators perform the integration after which the update causes an interrupt. Then the data in all 16 correlators of all 64 boards are sequentially read by the computer. The computer does not read directly from them. The update causes the correlator data to be outputed to intermediate data collectors ( one for each 8 correlator rows ).

And finally data stored in these intermediate storage are outputed to a central output collector through hardwired circuits. The computer then reads data from this collector.

The selection of correlator cards is done using a 6 : 64 decoder circuit comprising of two stages of 3 : 8 decoders. The first stage selects the row of cards to be read and the second stage which has eight 3 : 8 decoders, one for each row selects individual correlator cards on each row. Once a correlator card has been selected additional hardware allows the output data from every one of the 16 correlator (VLA 2) present on each card to be read sequentially into the collector.

This data collection process is performed for all the 64 cards once every update pulse occurs and data is stored in the central output collector. The computer then reads data from the central output collector before continuing the post integration.

#### CONTROLLER

a) It is the interface between the computer output and the inputs of the correlators, delays and samplers.

b) It provides the necessary timing signals and programming information to the system. c) It provides the necessary signals for the computer to read the correlator outputs.

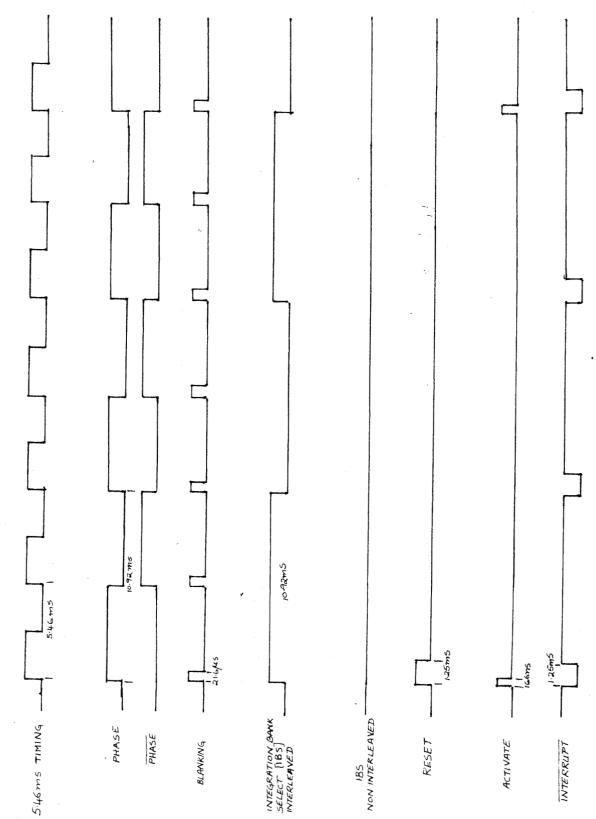

The correlators and the delay lines need a clock, a phase switch signal and a stop switch signal at the end of each integration time. They are provided by the controller. The phase switch signal has a phase switch period of 10.92 ms.

The three phase switch signals are :

| PHASE ( CX )    | - Switches sign bit of the microprocessors.  |

|-----------------|----------------------------------------------|

| PHASE ( SQ )    | - Switches modulators at delay line outputs. |

| PHASE ( Walsh ) | - Wired separetely to each delay line input. |

| 6               | Orthogonal phase switch patterns ( Walsh     |

|                 | functions) can be provided for the delay     |

|                 | line.                                        |

#### MODE OF OPERATION AND TIMING

The system is designed to operate with high time resolutions, therefore integration intervals have to be contiguous. This that different levels of operations such as requires programming, system configuration, delays, integration, transfer of data, etc, have to run simultaneously. To meet this demand the microprocessors controlling the correlators need to have two seperate register sets. One for integration and the other for This is controlled by integration bank select (IBS) readout. which alternates between integration intervals. signal The system has to be programmable without immediately affecting current operations. The information has to be presorted and activated by an internally generated command (Activate signal) This signal is not only used internally to activate a new system configuration and new delays. It also controls external, intermediate memories where information is used to steer the antenna arrays, the first LO synthesized (observing) frequency etc, precisely between integration intervals.

To avoid integration of transient signals after a change in configuration, the delay outputs are reset by a blanking signal at the beginning of an integration interval - every 10.92 ms or every integration interval input. It is estimated that the longest transient interval occurs after steering the antenna array and changing the delays, an interval of approximately 20 micro seconds.

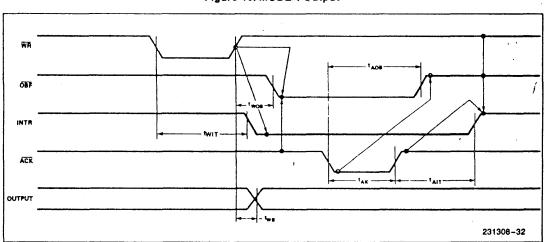

The following timing diagram shows the beginning of Integration intervals where the configuration has to be changed after the second integration interval.

#### GROUP A

It consists of three fixed timing patterns synchronous to the 16 basic timing pattern 2 / 12 MHz = 5.46 ms.

#### UPDATE SIGNAL PULSE

Update signal pulse loads the state of the preintegrator counter into the shift register and resets the counter after that interrupts the microprocessors, which in turn reads all the shift registers and accumulates them into the 16 bit registers. The IBS signal determines which of the two register sets (integration bank 0 or 1 ) has to be used with a positive or negative sign.

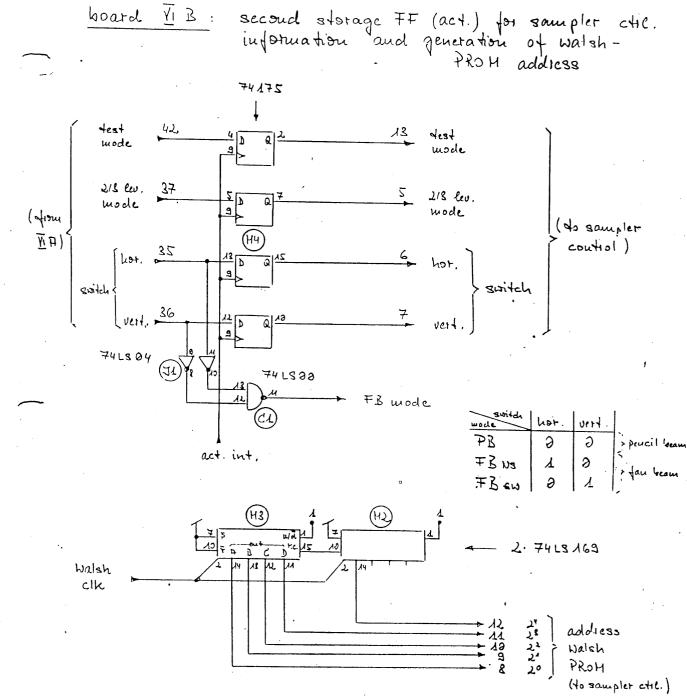

#### WALSH SEQUENCES

Walsh sequences are produced in a separate generator depending on the system configuration(PB, FBNS, FBEW) clocked by the basic timing pattern. They control the inversion switch in the second LO inputs to the receivers and in the outputs of the sampler units.

#### BLANKING SIGNALS

To simplify the blanking concept a blanking interval is sent every 5.5 ms, synchronous to the basic timing pattern. This assures that the positive and negative phases are equally shortened and any possible transient phase is covered. The blanking interval is (256 / 12 micro seconds = 21.3 micro seconds ) Therefore it only reduces the maximum possible integration interval by approximately 0.4%. This is in addition to a 0.1% reduction due to the gaps between the update intervals.

#### GROUP B

These consist of signals from the computer that affect the timing of the signals in group C

#### INITIALIZE

Initialize causes the system to generate a reset and activate pulse at the next clock of the basic timing pattern ( within < 5.5 ms). It also causes the Phase and the IBS signal to go or to stay low. The reset pulse goes directly to the microprocessors directing it to clear all the accumulators. The Activate pulse brings the system configuration A ( programmed anytime before the initialize signal ) into effect. The phase signal will now regulary change with every clock of the basic timing pattern. The IBS signal stays low during the integration

interval. The shortest interval is choosen. At the end of each integration interval the system generates an interrupt signal telling the computer to read the data from the previous integration interval in the bank 0. The IBS signal changes the second integration interval which immediately starts accumulating in bank 1.

#### MODIFY

In order to run the third integration interval with a different configuration, the modify signal has to be sent during the second integration interval. This causes the system to generate an activate pulse at the end of the second integration interval which brings configuration B into effect, which was previously programmed sometime between start of the first integration interval and the modify signal.

Reading the data from bank 0 or 1 always clears the accumulators. Therefore the reset pulse is only required at the beginning of the integration signals.

#### INTERLEAVED / NON-INTERLEAVED MODE

The mode of operation described is called interleaved. It requires a relatively fast data transfer to the computer, which for short integration intervals can only be acheived by direct

memory access ( DMA ).

To observe stationary radiating objects where high timeresolution is not required, in a simpler mode, the non-interleaved mode is used. To operate this mode, a special initialize signal is sent which causes the IBS signal to stay high after the first integration interval until after the next initialize signal is sent. No further interrupts are sent to the computer , therefore the computer can read the data from bank 0 at any desired speed.

i

MODIFY/RESET CODE

B I T - Dept of Electronics and Communication 1990 - 91

ę

SYSTEM CONFIGURATION CODE

## THE EXISTING SYSTEM

#### EXISTING SYSTEM

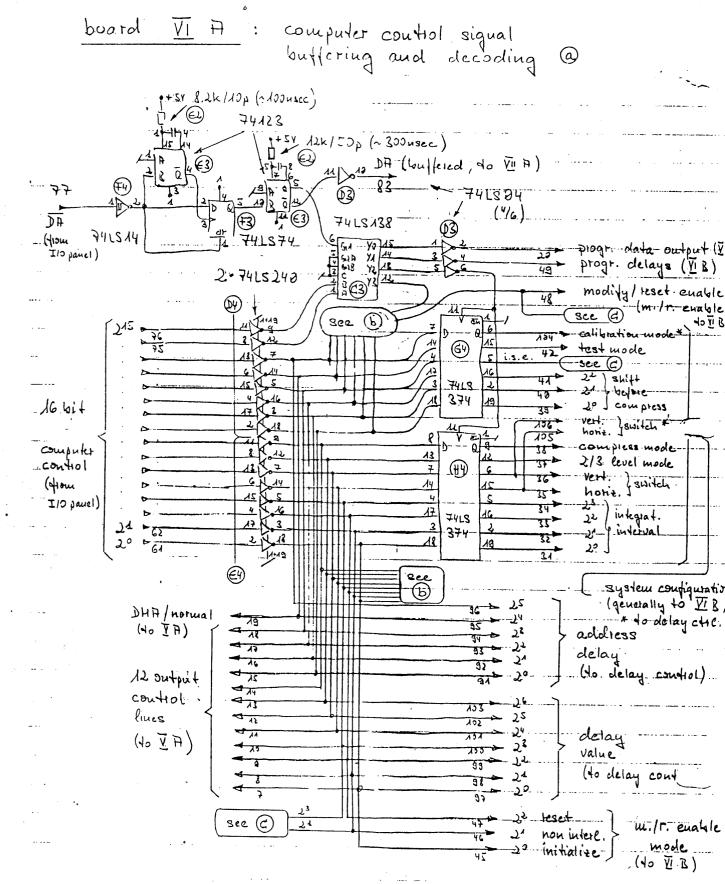

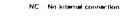

BOARD VI A - Part(a)

Data lines which are connected to this board are numbered from 61 to 77. The data bits comes in from the input/output panel. DA is a signal which also comes in from the input/output panel. This signal is delayed and routed to enable the three line to eight line decoder (74LS138) to allow enough time for bits on the lines 61 to 76 to settle to their correct values, at the inputs of the octal D flip-flop (74LS374).

The working of the boards VI A - Part (b), VI A - Part (c) and VI B boards depends mainly on the programming and status words entered in the System configuration code. A list of all the codes appear in the introduction. It is observed that lines 15 1675 and 76 (2 and 2) play an extremely important part in the in the implementation of the various codes.

Since the output lines of the 74LS138 ( Chip C3 ) are active / low, the outputs from this chip - Y0 to Y3 are inverted outputs. Y3 goes noninverted to Board VI A - Part (b).

The delay programming code which is not handled in VI A and B are channelled to the delay control from the 74LS374 latch inputs.

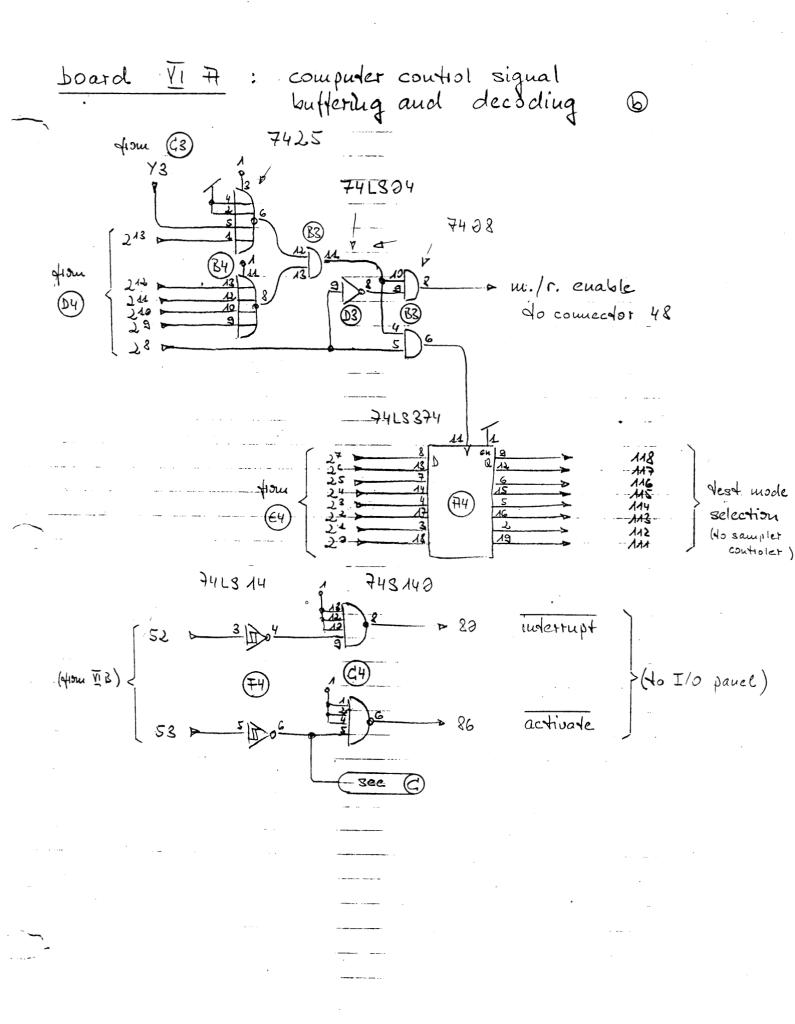

BOARD VI A - Part (b)

When activated these circuits output a modify/reset enable bit or clocks Test mode selection data to the Sampler Controller.

9 13 If any one of the data inputs (2 to 2) and Y3 are 1 then neither of the outputs are activated.

When all of the above mentioned data inputs are 0 then the 2 input decides which of the two outputs to activate - A 0 value  $\frac{8}{1000}$  for 2 enables the a modify/reset output and a 1 enables the test mode selection output, which in turn, outputs test mode selection data to sampler controller through a 74LS374 latch.

When a new system configuration code is to be sent, the 2 15 and 2 ( pin no. 75 and 76 ) are entered with 0 and 1 respectively. This enables the rest of the data from pins 61 to 74 to be latched to the appropriate points of the various circuits. The latches being chips G4 and H4 on VI A - Part (a).

#### 14 15

14

When both pins 75 and 76 (2 and 2) are made 1 and pins 8 13 69 to 74 (2 to 2) are made 0 then the resultant at Y3 (Chip C3 - 74LS138) is an active low signal and the 0's at pins 69 to 8 13 74 (2 to 2) generate the modify/reset enable signal which in turn activates appropriate signals in board VI B.

Pins 61 to 68 ( $2^{4}$  to  $2^{'}$ ) are also 0's and are gated to the Sampler control (Board VIB - Part (f)).

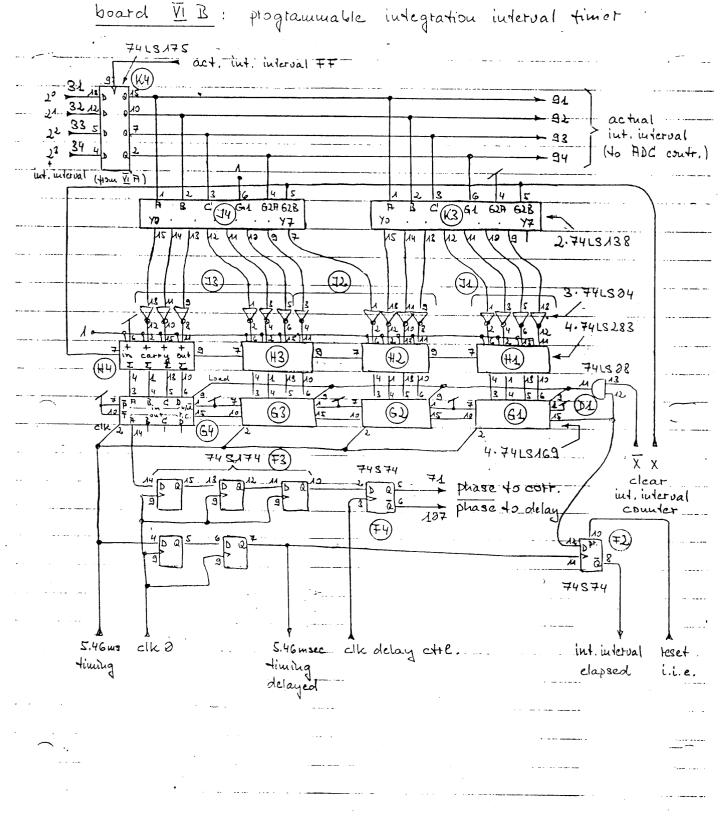

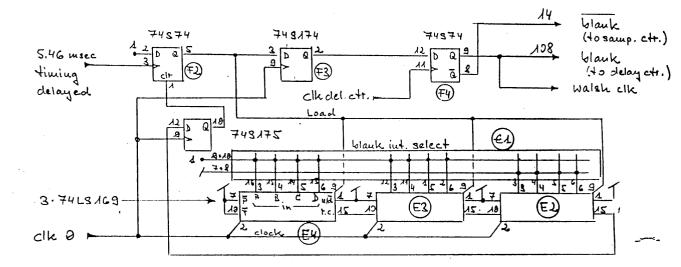

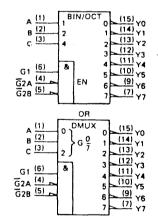

BOARD VI B - Part (a)

The programmable integration interval timer sets the timing interval for the integration taking place in the correlator.

A rising edge at clock input of Chip K4 outputs the integration interval data on lines 91 to 94. The 74138's (Chip J4 and K3 ) are so connected that Chip J4 is activated for all integration values from 0000 to 0111.

The 'Clear integration interval counter' - line X should be at 0 for 74LS138's to be enabled. Both X and  $\overline{rc}$  ( ripple carry out pin 15 ) of Chip G1 are at 1 during counting. This disables the load inputs to the 74169's and enables count operation to go on.

The actual integration interval (Z) is decoded from the integration interval code (n), using the formula n+1Z = (2 - 1) X 10.92 ms. where n = 0, 1, 2, ...,14.

Thus the smallest integration interval is 10.92 ms. For non zero values of n the counters count down the decoded integration interval with the 5.46 ms clock.

At terminal count when chips G1-G4 reach 0000 the  $\overline{rc}$  output pin 15 of G1 disables the counters and chip F2 the flip-flop converts the negative going  $\overline{rc}$  (ripple carry-out pin 15) to a

positive pulse after sufficient delay ( 5.46 ms ). This signal is called integration interval elapsed ( IIE ).

Should a modify signal occur between two IIE's, the line X goes low disabling the counters from counting and loading the new integration interval into the counters from the adder outputs. At the occurence of the  $\overline{rc}$  output the IIE is signalled and the count down process for the new integration interval begins.

When no modify signal occurs the ripple carry output reloads the unchanged integration interval from the adder output into the counters and when rc goes high count is enabled.

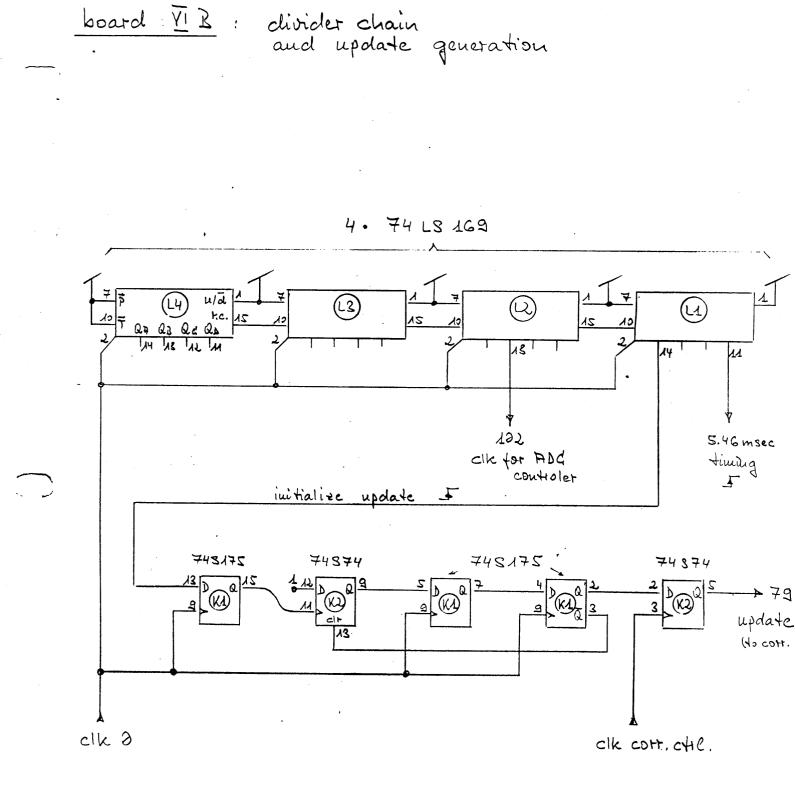

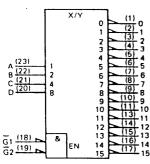

BOARD VI B - Part (b)

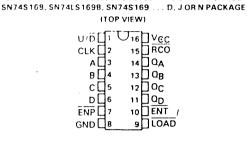

A basic clock frequency of 12 MHz clocks the 4 counter cascade (74LS169 - Chips L1 - L4).

The basic integration clock is tapped at pin 11 of chip L1 (the MSB of cascade). This pin 11 corresponds to the divide by 16 2 output which yields a 5.46 ms clock.

As the multiplication and accumulation involved in the correlation involves repeated addition by an offset value of 1, a counter is necessary whose value is incremented by 0,1 or 2 depending on the product of 2 bits.

This preintegration counter has a maximum capacity of 14

bits. If a worse case is imagined where 2 is added to the counter 14 value, the counter would overflow at the 2 clock pulse.

13

Therefore after every 2 th clock pulse, the value of the 14counter must be stored, before the 2 th clock pulse occurs an overflow would occur. This value is moved into a string of shift registers and the counters are reset with an update pulse of width 2 x 83.3 ns = 166.6 ns. This pulse also causes an interrupt to the microprocessor which the contains the integrated data and then reads the 12 bit shift register whuch holds the result of an integration over an interval and further integrates them into 16 bit values. and accumulates them into 16 bit registers.

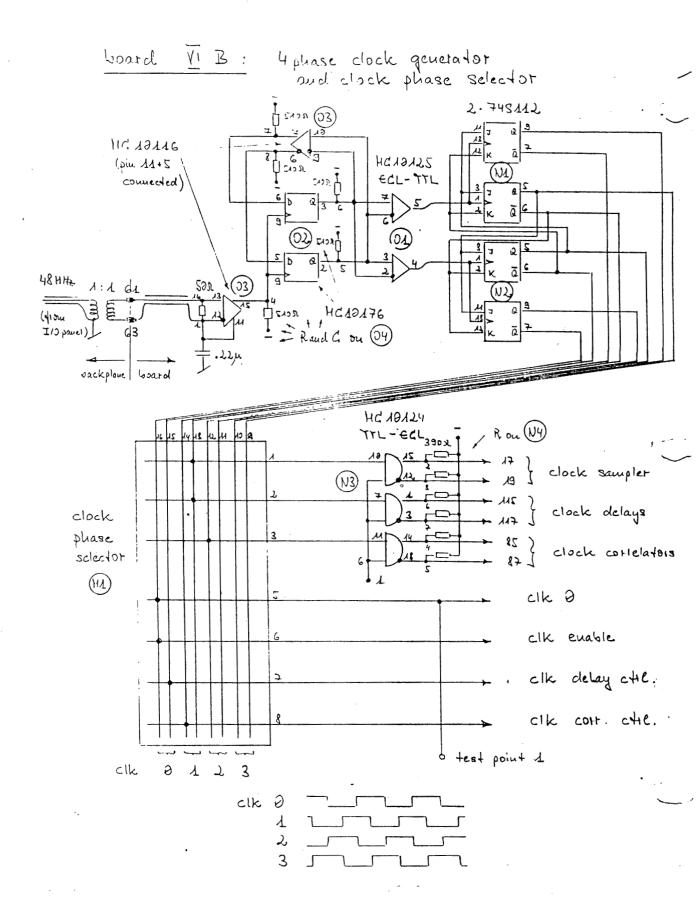

BOARD VI B - Part (c)

A 48 MHz oscillator output is available from a 1:1 transformer. The oscillator is located on the input output panel.

The 48 MHz output is used to generate 12 MHz clocks which clock the various circuits on VI A and VI B and also on the various controller boards.

This is done by dividing the 48 MHZ into four, 12 MHz signals. Now each 12 MHZ clock is 90 degrees out of phase with respect to each other, resulting in a 4 phase clock.

The output of the transformer is fed to Chip O3 ( HC 10116 ) and later to ECL D-flip-flops HC 10176 (Chip O2 ) These pulses

are then converted from ECL levels to TTL levels with the help of Chip O1 (MC 10125). After this four JK flip-flops which are interconnected as in the circuit and generate the clocks in four phases.

Further chip N3 (MC 10124) converts TTL levels to ECL levels, this conversion is necessary as clocks in ECL levels are also required for the samplers, delays and correlators.

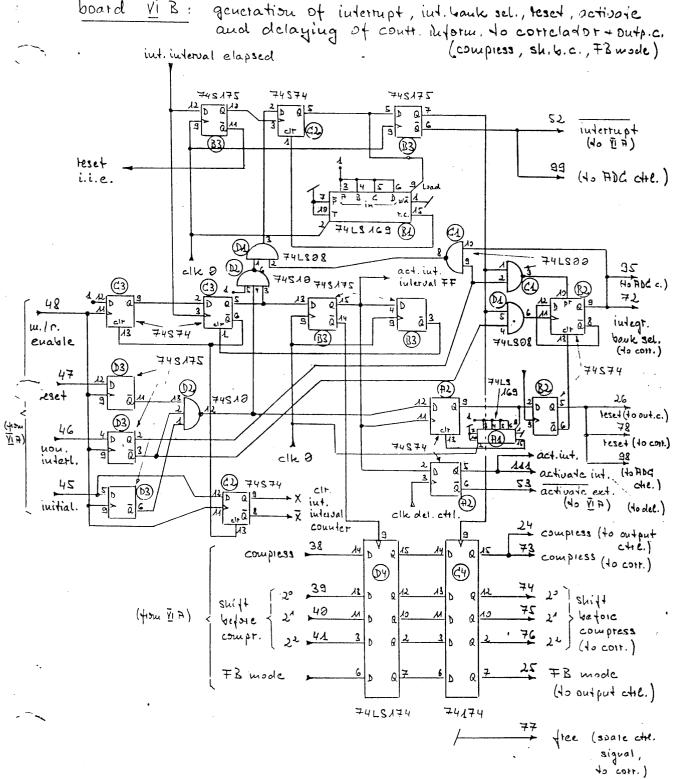

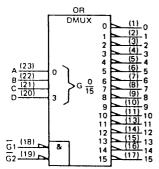

BOARD VI B - Part (d)

The three key bits that control the operation of the 0 correlator system are the initialize (2), the 1 2 interleaved/noninterleaved (2) and the reset (2).

This circuit receives these latched bits and generates appropriate signals to control the mode of functioning of the correlator. These signals are the interrupt, the IBS, the reset and the activate.

A change in system configuration made in between two integration intervals is implimented by the system only at the end of the current integration interval. The integration interval elapsed signal from VI B Part (a) (which signals the end of every integration interval ) is therefore used to actually generate appropriate signals for the bits 2 , 2 and 2 . These bits are latched into the circuit whenever there is a change in modify/reset code through the m/r enable. The difference

between initialize signal and reset signal is that initialize causes reset, activate to be generated and causes IBS to go low before integration interval elapsed occurs. When reset is 1 integration elapsed signal is generated.

|                     | IIE 1                                         | IIE 2 &-by<br>all subsequent IIE's                    |

|---------------------|-----------------------------------------------|-------------------------------------------------------|

| reset = 1           | generated by                                  | generated by                                          |

| noninterleaved = 1  | generated by<br>IIE 1                         | generated by<br>IIE 2 only                            |

| Initialize = 1      | generated<br>immediately                      | generated by<br>IIE 1 & all<br>other subsequent IIE'S |

| 0 2<br>2 - 2 of m/r | IBS goes low<br>activate & reset<br>generated | interrupt generated &<br>IBS switched                 |

BOARD VI B - Part (e)

The smallest integration interval is 10.92 ms. The phase switch inverts once every 10.92 ms, and phase switching takes place every 5.46 ms.

Any change in system configuration may give rise to B I T - Dept of Electronics and communication 1990 - 91 transient signals and care must be taken to see that these signals are not integrated. Again transient signals may also arise after every phase inversion which occurs every 5.46 ms as both + ve and - ve phases must be symmetrically blanked so that the amount of data accumulated ( in the microprocessor ) during +ve and -ve phases are the same. the 2 phases.

To avoid such an integration of spurious signals, the blanking pulse is generated every 5.46 ms which zeros the delay outputs so that (although the integration interval clock is on ) the integration does not take place during this time. As the longest interval for which transients can occur is about 20 micro seconds, in the circuit the blank pulse is 21.6 micro seconds long.

The basic 5.46 ms pulse clocks a high to the output which through a counter cascade selects the blanking interval forces down the high after 21.6 micro seconds ( by a divide by 8  $\frac{8}{2}$  configuration 12 MHz / 2 ). The blanking pulse therefore lasts 21.6 micro seconds and occurs every 5.46 ms.

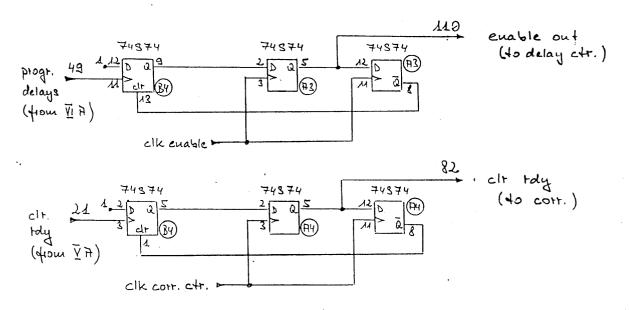

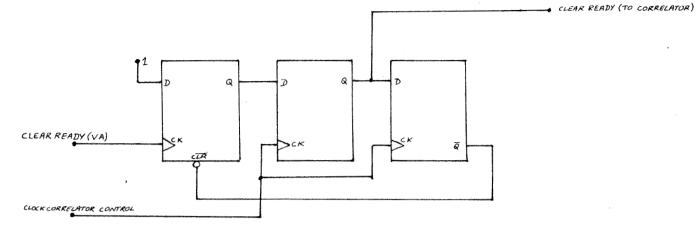

A pulse synchroniser circuit synchronises the programable delays input and Clr.rdy input with the basic 12 MHz clock.

BOARD VI B - Part (f)

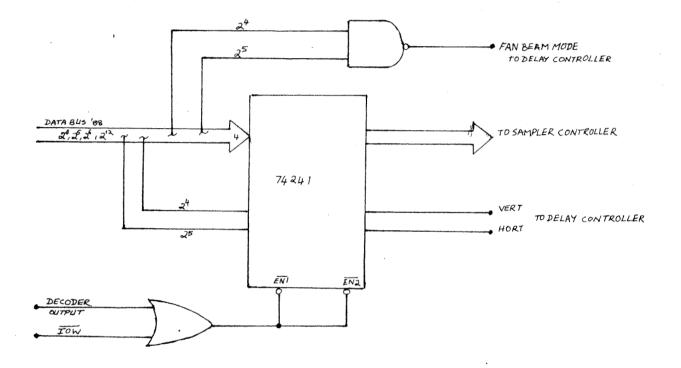

4 5 6 12 Bits 2, 2, 2 and 2 of system configuration code are

channelled for sampler ane delay control.

The outputs to the sampler control are 2, 2, 2 and 2 which are latched out only on the arrival of the ACTINT signal 4 5from VI B - Part (d). 2 and 2 are also output to the delay control. In addition to this the delay control also receives an 4 5AND'ed output of 2 and 2 which specifies whether the system should work in fan beam or pencil beam mode.

.

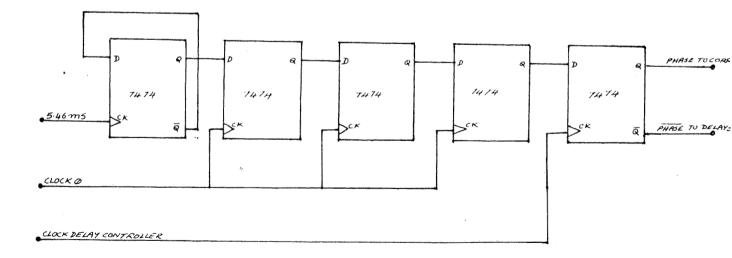

VIB: generation of interrupt, int. Lank sel., teset, activore

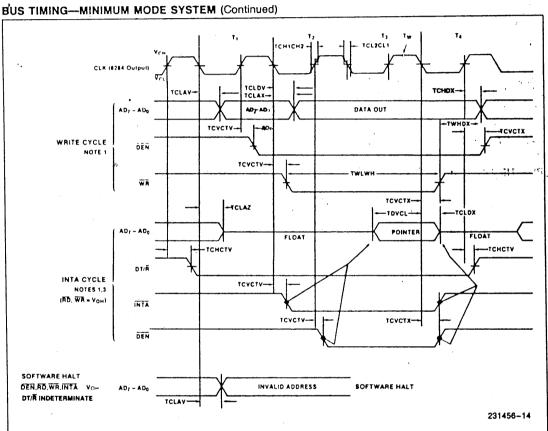

board VI B : diming Shows Aransitions at gap between in tegration intervals, actual Hausition times depend on clock phase selection : 88. Susec CIK 2 activate int. (Lafter 27) (Duly after m. Ir. code) 12 1 /0 blank (Lafter < 4096T) cik delay ctr. 12 r (every 5.46 mscc) phase χĩ XI Э (changes every S.46 msec). { } t beginning of integr. interval to { cott. } starting with updade (Lafter 27) /12) (every 682.7 usec) teset (Latter 157) (2) / 2 л cik corr. ctr. (ouly after w. /t. code \_\_\_\_\_\_ with bit 2 or 1 or 2 Esg. 1) integr. bank select - interleaved mode (2) Y Э - after reset (both modes)\_ - after int. - interval in non interleaved mode compless + shift Gefore cru. (changes offer int. int. according to programing) interrupt (J after 15T) (only after integr. interval)

## THE PROPOSED SYSTEM

## PROPOSED SYSTEM

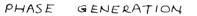

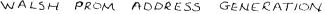

The system clock operates at a set frequency of 12 MHz. The generation of this clock frequency is done by a 48 MHz local oscillator, located in the correlator unit.

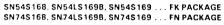

This signal is first converted into a proper square wave by using an operational amplifier comparator chip - the NE521. The output is then fed to a divide by four arrangement called the four phase clock generator, which basically consists of a chain of three, hex D flip-flops (74F174).

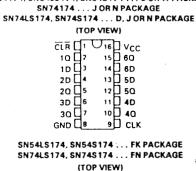

As four phases of the resultant 12 MHz clock is required, the flip-flop chain is tapped at 4 output points and the driving capability of the four phase signals are enhanced by a 74F365 line driver.

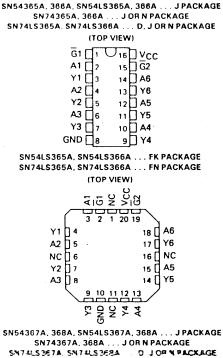

As the sampler, delay and correlator boards contain ECL chips, the four clock phases are level shifted from TTL to ECL levels using the MC10124 - TTL to ECL interface chips.

As a set of clock phases is required for the proposed system, which operates at TTL levels, one set of clock phases are thus retained, at TTL levels.

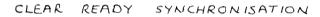

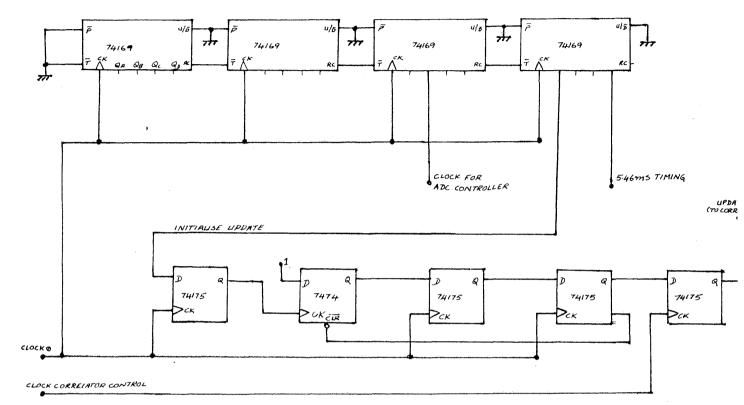

The basic integration interval of the correlation process is 10.92 ms. The 5.46 ms waveform is generated from Clk 0 using a

divide by 2 circuit as shown comprising of four 74LS169 chips. The 5.46 ms timing is obtained at the MSB of this cascade.

The Update signal occurs once every 2 clock 0 cycles that is once every 682 micro seconds. Therefore the Update signal is tapped at the 13th output of the divider chain and is delayed by 166 ns seconds before it is synchronised with Clk Correlator Control and sent to the correlator system. This delay is introduced using a chain of 74S175 and 74S74 flip-flops.

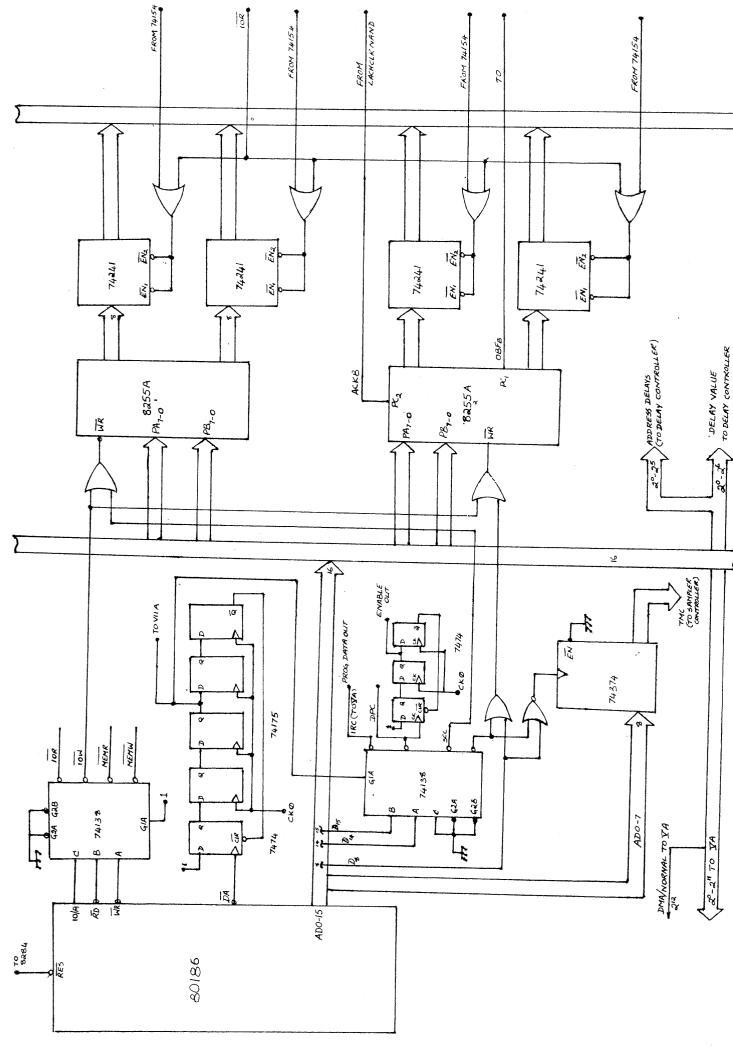

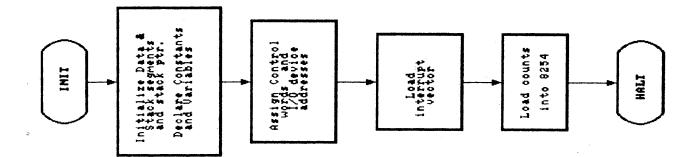

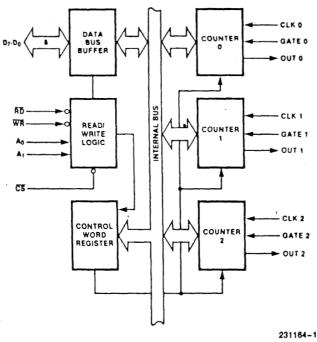

The 80186 has three functions:-

- a) Acquires data from the correlator matrix.

- b) Programmes the correlator/delay system through the 8088 system.

- c) For power system monitoring.

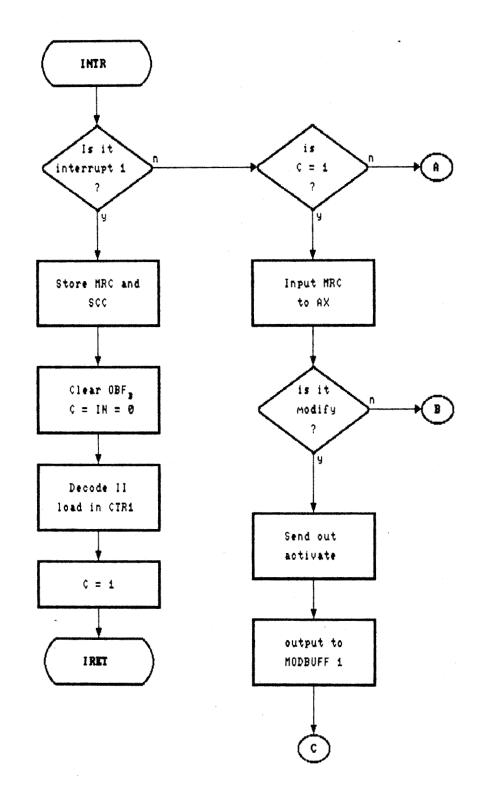

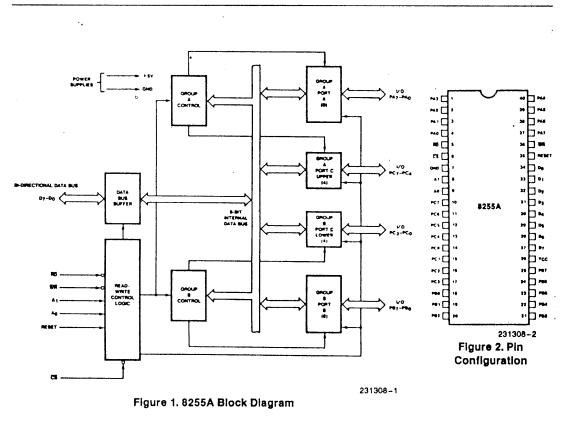

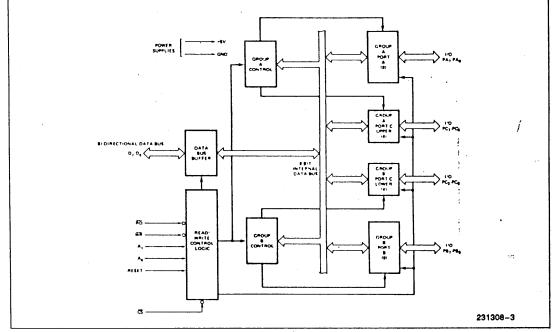

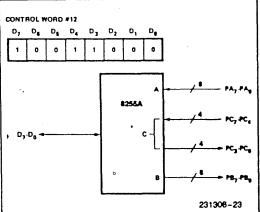

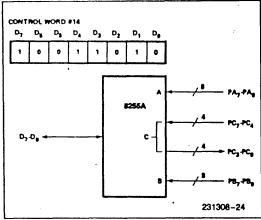

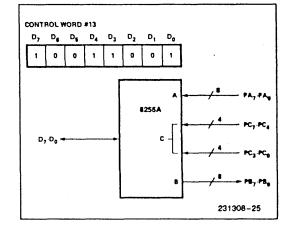

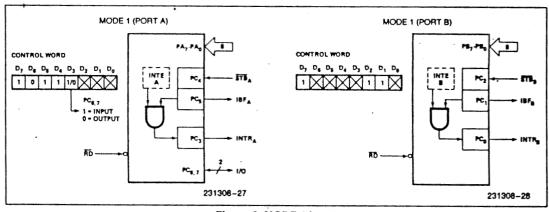

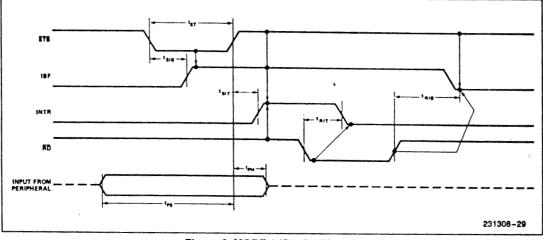

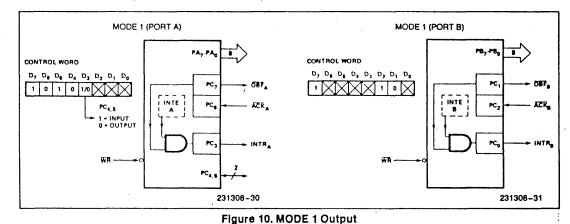

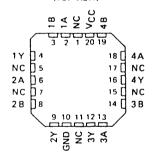

The outputing of the SCC ( system configuration code ) and the MRC ( modify/reset code ) from the 80186 to the 8088 is accomplished through two programmable peripheral interface chips 8255A ). Ports A and B in both chips are programmed by ( the 80186 software to operate in mode 1 ( strobed output ). In this mode the OBF pins of the 8255A go low as soon as the data 18 written into its port. The OBFb of the MRC 8255A interrupts the 8088 through the 8088's INTR pin. This ensures that both SCC and MRC have been transfered entirely before the interrupt to the 8088 is actually made.

B I T - Dept of Electronics and Communication 1990 - 91

16

In the interrupt service routine the 8088 reads the four ports by seperately adressing four tri - state buffers (74241). After this it generates an  $\overline{ACK}$  signal to clear the OBFb pin.

To ensure that the 8088 has received the codes, the 80186, after writing out all the codes, polls bit PC 1 of the MRC 8255A until it senses a logic 1 or a high bit. This indicates that the ACK signal has arrived and therefore the codes have been read. The 80186 software may be written so that it polls the PC 1 bit for only a predetermined period of time. Withen this time if the poll is unsuccessful the 80186 may write out the codes again.

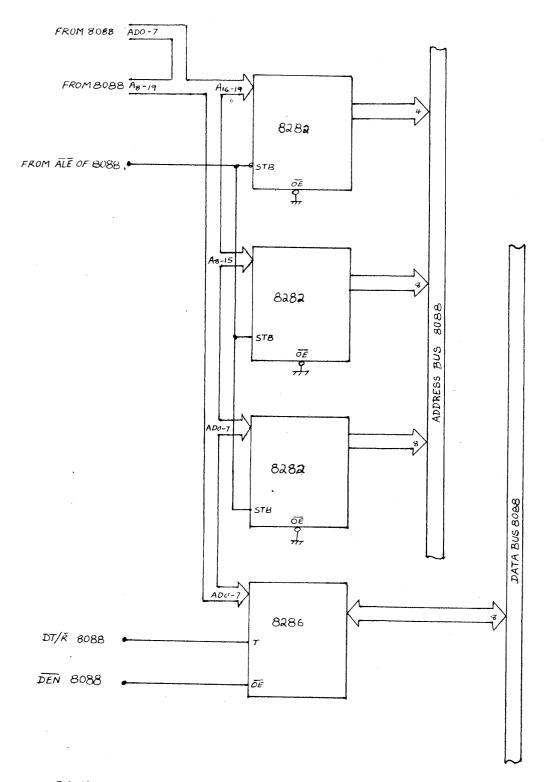

An 8286 chip has been used as a parallel bi-directional bus driver for the 8088 data bus. The 8088 DEN is connected to the OE of the 8286 and eliminates bus contention and the  $DT/\vec{R}$  ( of the 8088 ) to the T ( 8286 ) determines the direction of data flow. T is sent low to receive data and is high if data is to be sent.

The 8282 I/O ports are used as address latches for the 8088. The OE pin is permanently at ground and the address is enabled into the 8282 using the  $\overline{ALE}$  of the 8088 to the STB of the 8282. There are three in all, to latch the 20 bit address.

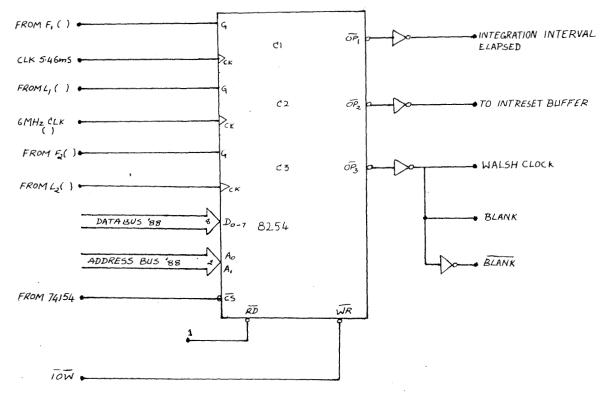

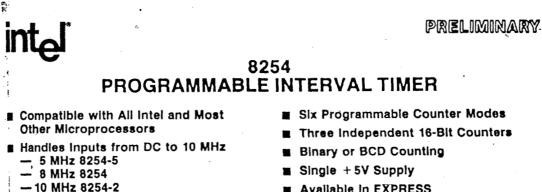

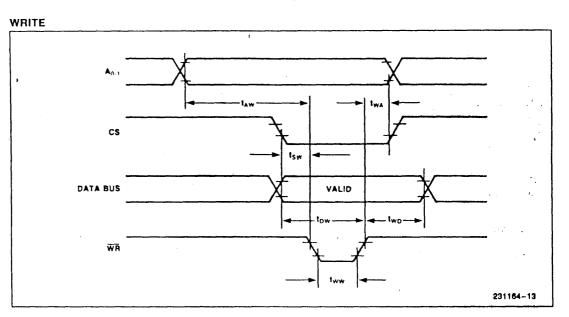

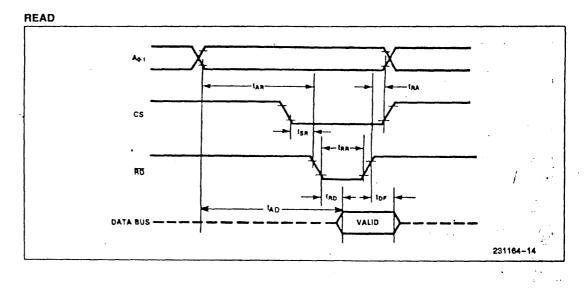

The 8254 select inputs are AD3 - AD0 and its chip select pin is enabled by an I/O device decoder circuit in accordance with the address mapping of the I/O devices, i.e. OF00 being the decoder chip select combination and A3 - Ao enable the particular

I/O chip pin of the 74241 (tri state buffer) whose input is hard wired to 08h, the interrupt type. When the INTA signal is generated the interrupt type is read from which the interrupt pointer is calculated and using the CS and IP contents stored therein the interrupt service routine is acessed.

There are two interrupts in this sub system,

1) Interrupt 1 ( INT1 ) to signify a change in system, modify/reset code.

2) Interrupt 2 ( INT2 ) to indicate the occurance of an integration elapsed signal.

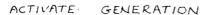

As the first is a level and the second is a pulse it was decided to use a 74LS74 ( D flip-flop ) with an associated circuitry which latches the interrupts ( when either occurs ) to the flip-flop output. The 74LS74 output therefore forms a 'Interrupt Word' which is read by the 8088 as soon as an interrupt occurs. The interrupt is identified ( as INT1 or INT2 ) by the 8088 software. A 74LS241 - non inverting tri state buffer which is enabled by the 8088 using I/O addressing, to read the interrupt word.

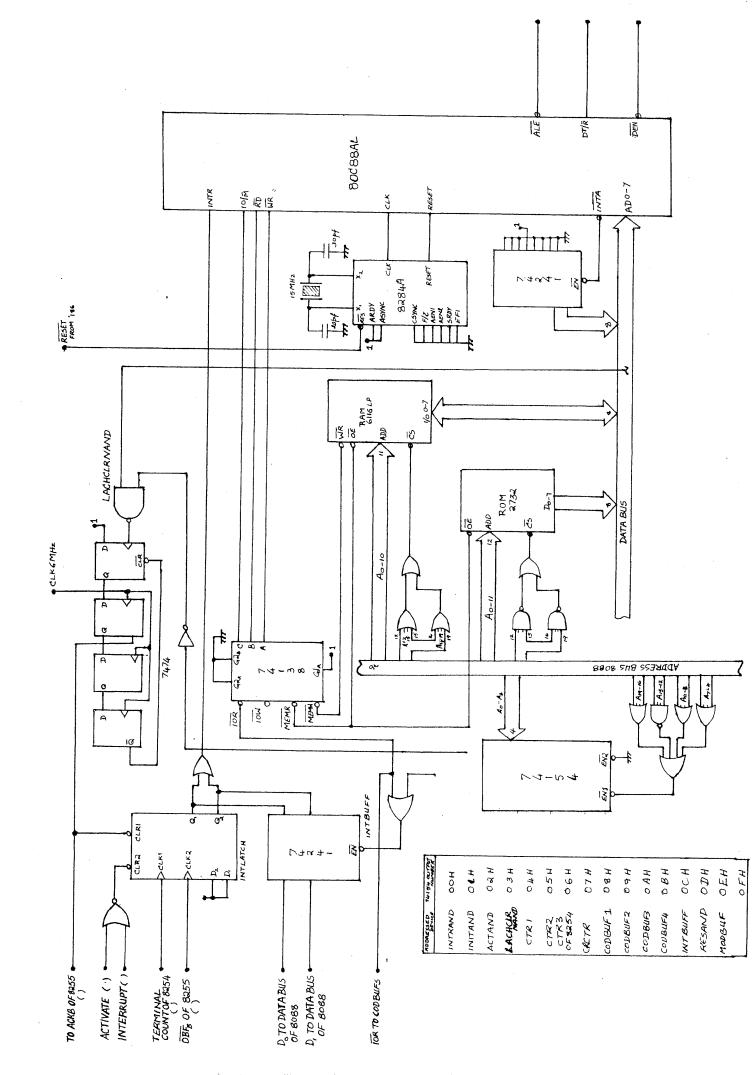

The work of the circiut in VI B (a) is to handle the task of decoding and counting down the entire integration interval and then signalling an integration interval elapsed to the rest of the system. It was decided to replace this circuit with a combination of hardware and software. The hardware is the 8254 timer chip, and it counts down the integration interval. The

signalling and decoding of the integration interval is done in the microprocessor itself in its software instructions. The software also handles the loading of the current integration interval value into counter 1 of the 8254.

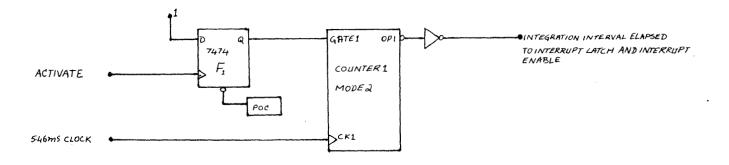

The basic timing of the integration process is the 5.46 ms clock. This is therefore the clock input to the counter 1.

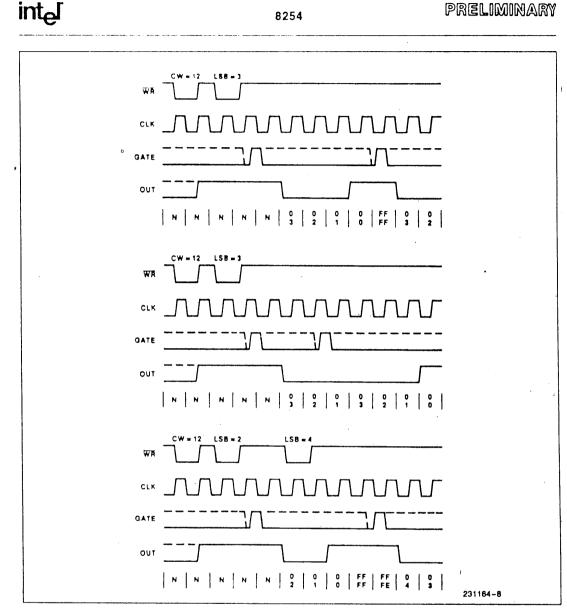

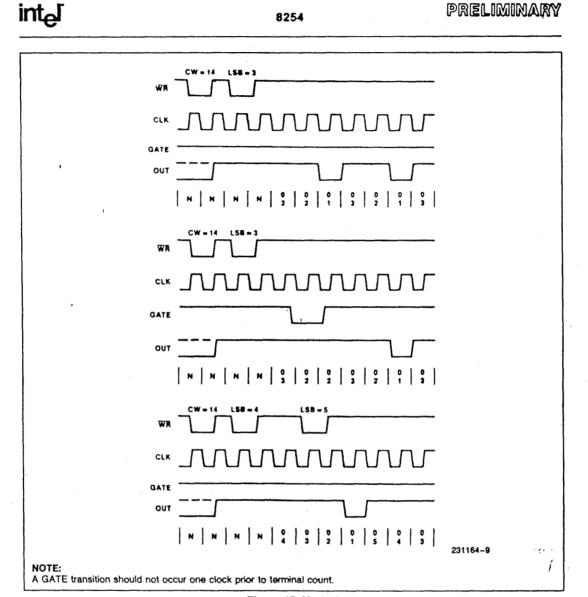

The D - type flip-flop at the gate of counter 1 has a power on reset connection to it. This ensures that at the beginning of the operation counter 1 does not begin counting from any random number its count register might hold. Again, keeping the gate tied high would enable counting before the interrupt 1 occurs. This would disturb the entire system sequence of operation and its performance. The gate is at low level from the beginning of operation till the time the first Activate pulse is generated, i.e. - until the first set of System configuration and modify/reset codes are input. This pulse clocks the gate which enables the count. This counter is operated in mode 2, that is, it functions as a rate generator. The mode 2 is specified in the counters control register contents ,which is loaded into the 8254 at the beginning of operations.

The output pin is connected to the interrupt latch and to the interrupt enable.

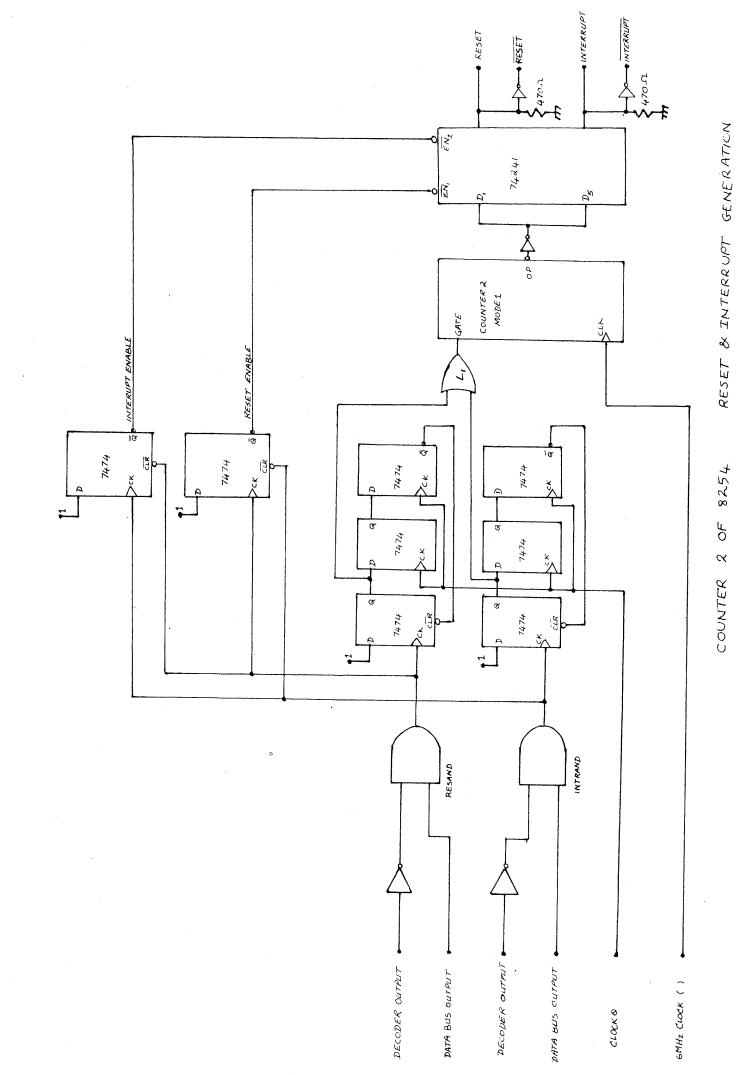

Counter 2 of the 8254 generates the reset or interrupt pulses. The same count is loaded into the count register for

both signals as both have the same pulse width of 1.3 micro seconds. The closest pulse width obtainable to this using its 6 MHz clock is 1.44 micro seconds. The 6 MHz clock is obtained from the first output pin of the divider chain (in VI B (b) ). The count loaded is 09h.

The counter operates in mode 1 and therefore functions as a programmable one-shot whose output pulse width is a product of the count and the clock's time period .

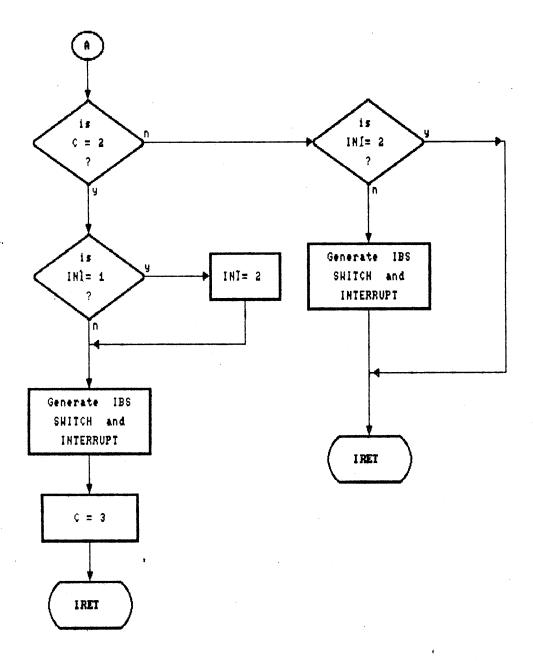

The gate input to this counter is an OR'ed output of the RESAND and INTRAND. This is because the same output pulse from the counter functions as two different signals. The reset is channelled to the output controller, the correlator and ADC controller. The negated reset serves to pull the IBS to 0 through a connection to the clear pin of the IBS flip-flop. The RESAND output goes high whenever there is an MRC change.

As the same output functions as two different signals at different times. A 74LS241 has been used to explicitly identify the pulse as a reset or an interrupt as the operation demands.

The output of counter 2 is input to two buffers ( of the available eight ) in the 74LS241 chip. Each is controlled by a separate enable pin. When the configuration requires a reset pulse to be output, the enable of the corresponding buffer is activated and simultaneously the buffer which channels the

interrupt pulse is disabled, and vice-versa. The reset has been used to enable one buffer and disable the other. Likewise the INTRAND output is always high for an interrupt signal to be generated and therefore used to enable the buffer for interrupt and disable the one for reset.

All signal generation in this subsystem is microprocessor controlled (by software). Whenever operation protocol demands, the reset, activate interrrupt and the IBS signal have to be directly generated by the software. One way to do this is to use two-input AND gates as separately addressable output devices. The I/O decoder enables the chosen AND gate . A high on a uniquely chosen data line produces a high output which either clocks the necessary flip-flops or enables the concerned gates to generate the necessary signals.

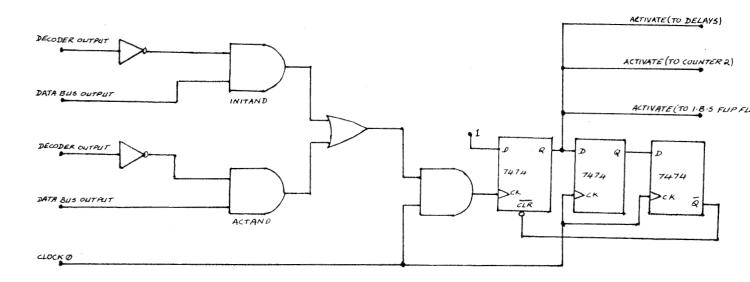

The activate signal signifies a change in the operating mode of the telescope to the various components of the digital system.

The pulse width of the activate signal is 166 ns. This has been retained in the proposed system along with the flip-flop circuit which generates it. Three D flip-flops are connected to constitute a shift register with the MSB flip-flop's  $\overline{Q}$  is fed back to the clear input of the first. The activate is generated by the system whenever the initial bit in the modify/reset code is high or otherwise whenever there is a change in system configuration. The INITAND and the ACTAND which respectively signify the above conditions are both OR'ed before they clock the

activate generation. To ensure that the activate pulse is not shorter than 166 ns, the OR'ed output is AND'ed with CLK O before the AND output initiates the activate generation.

• The ACTAND output goes high only after the occurence of the IIE signal (integration interval elapsed - which is sensed by the microprocessor ) or when there is a modify signal. The INITAND output however, goes high immidiately after the modify/reset code has its 2 bit high. The activate generation in this case does not wait for the IIE to occur. The IBS (integration bank select ) is cleared to 0 at the advent of every reset signal and toggles at the occurence of every interrupt signal. This is achieved by using a D-flip-flop ( called the IBS flip-flop ) connected in toggle mode, clocked by the by the interrupt signal and cleared by the reset signal.

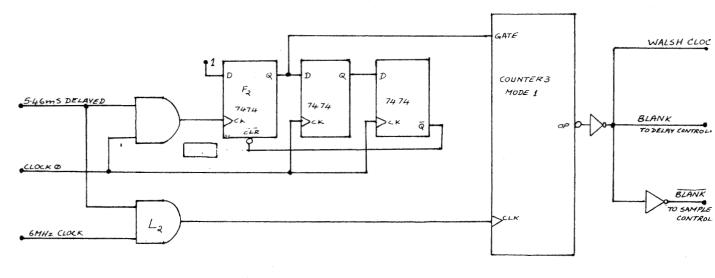

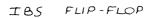

The blank signal should occur a few nano seconds after the 5.46 ms clock's rising edge. To ensure this and keeping in mind the 21.3 micro second pulse width of the blanking pulse ( < 5.43 ms ) itself, it was decided to AND the 5.46 ms delayed clock with a 6 MHz clock ( from the divider chain ) at the clock input of the 8254's third counter.

As the gate pulse to the counter is specified to be of a minimum of 150 nano seconds, a 166 nano second gate pulse is generated using a CLK 0 and three flip-flops (7474 type ). This flip-flop chain has an AND'ed clock input of CLK 0 and the 5.46 'ms delayed signal. This ensures that the counter is enabled

through the gate, every 5.46 ms. The 5.46ms delayed clock is derived from two 7474 flip-flops connected in 2 bit shift register mode. A count of 128 ( binary ) is loaded into the third counter's count register during initilization and remains unchanged throughtout the system operation.

The output of the negative going pulse which is tapped for the sampler controller. An inverted pulse functions both as a Walsh clock and as the blank to delay controller.

The phase signal which is equal to the smallest possible integration interval (10.96 ms) is generated in both inverted and noninverted versions by a D-flip-flop in toggle mode or divide by two mode. This output is suitably delayed using flipflop register before the phase signal is sent to the correlator and inversion is sent to delay.

Pulse synchronisation is achieved (VIB (e)) for both the clr.rdy ( clear ready from VA ) and program delays ( from VIA ) with clock correlator control and the clock enable respectively. The programmed delays is the clock input to a D-flip-flop ( 74874 ) with the D pin tied high. This flip-flop is followed by two other flip-flops connected in as a 2 bit shift register, clocked by CLK Enable. A  $\overline{Q}$  fedback to the clear of the first flip-flop ensures that the enable out pulse to the delay controller is of 166 nano second maximum width.

A similar connection for the Clr.rdy signal from board V A

ensures that the Clr.rdy pulse to the correlator is a maximum of 166 nano seconds. Four output bits - test mode, 2/3 level mode, horizontal switch and vertical switch are channelled to sampler control through a seperately addressable 74241 buffer. Further, the horizontal and vertical switch bits have to be sent to delay control also. These are tapped from the buffer inputs and are sent to delay through the buffer itself. A NAND'ed output of the vertical and horizontal switch bits specify whether or not the fan beam mode is operating. This output is also sent to the delay.

## DATA BUFFER FROM 8088

THE PROGRAMMABLE INTERVAL TIMER

COUNTER 1 OF 8254

INTEGRATION INTERVAL COUNTER

•

.

.

CLOCK DELAY CIRCUIT

DIVIDER CHAIN AND UPDATE GENERATION

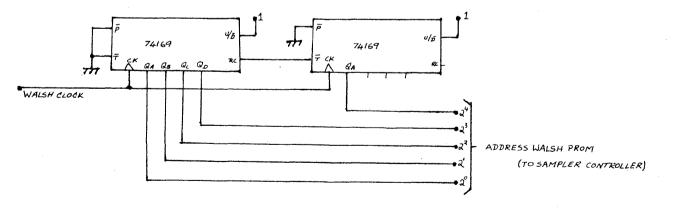

WALSH PROM ADDRESS GENERATION

4 PHASE CLOCK "GENERATOR AND CLOCK PHASE SELECTOR

- Dept of Electronics and Communication 1990 - 1991 BIT

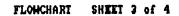

FLOWCHART SHEET 2 of 4

#### FLOWCHART SHEET 4 of 4

B I T - Dept of Electronics and Communication 1990 - 1991

----

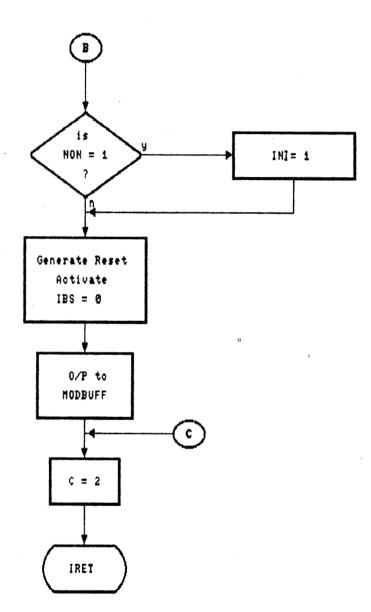

#### ASSEMBLY CODE FOR THE PROPOSED SYSTEM OF THE RADIO TELESCOPE

|         | initand      |                             | equ      | 0f001h       |     |                  |

|---------|--------------|-----------------------------|----------|--------------|-----|------------------|

|         | actand       |                             | equ      | 0f002h       |     |                  |

|         | resand       |                             | equ      | 0f00dh       |     |                  |

|         | lachclri     | hand                        | equ      | 0f003h       |     |                  |

|         | ctr1         | land                        | equ      | 0f004h       |     |                  |

|         | ctr2         |                             | equ      | 0f005h       |     |                  |

|         | ctr3         |                             | equ      | 0f006h       |     |                  |

| · 5     | crctr        |                             | equ      | 0f007h       |     |                  |

|         | codbuff      | 1                           | equ      | 0f008h       |     |                  |

|         | codbuff      |                             | equ      | 0f009h       |     |                  |

|         | codbuff      |                             |          | 0f00ah       |     |                  |

|         | codbuff      |                             | equ      | 0f00bh       |     |                  |

|         | intbuff      | +                           | equ      | 0f00ch       |     |                  |

|         | modbuff      |                             | equ      | 0f00ch       |     |                  |

|         |              |                             | equ      | 034h         |     |                  |

| ,       | cwctr1       |                             | equ      | 034n<br>052h |     |                  |

|         | cwctr2       |                             | equ      |              |     |                  |

|         | cwctr3       |                             | equ      | 092h         |     |                  |

|         | cntctr2      |                             | equ      | 009h         |     |                  |

|         | cntctr3      |                             | equ      | 080h         |     |                  |

|         | datintr      |                             | equ      | 01h          |     |                  |

|         | datinit      |                             | equ      | 02h          |     |                  |

|         | datresa      |                             | equ      | 04h          |     |                  |

|         | datlach      |                             | equ      | 08h          |     |                  |

|         | datresa      | nd                          | equ      | 010h         |     |                  |

|         |              |                             |          |              |     |                  |

| start : |              |                             |          |              |     |                  |

|         | mo∨          | ax, dat                     | a_seg    |              |     |                  |

|         | mo∨          | ds, ax                      |          |              | ;   | point ds to data |

|         |              |                             | •        |              |     | seg              |

|         | mov          | ax, sta                     | ick_seg  |              |     |                  |

|         | mo∨          | ss, ax                      |          |              | ;   | point ss to      |

|         |              |                             |          |              |     | stack seg        |

|         | mov          | sp, off                     | set tos  |              | ;   | init stack       |

| intvect |              |                             |          |              |     |                  |

| mevect  |              | ds                          |          |              | -   | aava da          |

|         | push         | ax, ax                      |          |              | ;   | save ds          |

|         | xor          |                             |          | ·            | ;   | 0 ax             |

|         | mov          | ds, ax                      | aat int  |              | ;   | 0 ds             |

|         | mov "        |                             | set int_ |              |     |                  |

|         | mov          |                             | set inin | t            |     |                  |

|         | mov          | [bx], a                     |          |              | ;   | store offset of  |

|         |              |                             |          |              |     | intr             |

|         | mo∨          | ax, cod                     |          |              |     |                  |

|         | mo∨          | [bx+2],                     | ax       |              | ;   | store reg.addr.  |

|         | <b>D</b> O D | da                          |          |              |     | of intr          |

|         | рор          | ds                          |          |              | . , | restore ds       |

| loadcw  |              |                             |          |              |     |                  |

| i caucw |              |                             | + ~ 1    |              |     |                  |

| 4       | mov          | al, cwc                     |          |              |     |                  |

| w_      | sout         | <pre> <crctr></crctr></pre> |          |              | ;   | load cw of ctr1  |

| ~       | mov          | al, cwc                     |          |              |     |                  |

| @_      | sout         | <pre> <crctr></crctr></pre> |          |              | ;   | load cw of ctr2  |

| ~       | mov          | al, cwc                     |          |              |     | <b>-</b>         |

| @_      | _sout        | <crctr></crctr>             |          |              | ;   | load cw of ctr3  |

|         |              |                             |          |              |     |                  |

.

|      | loadcnt :         |                                      |                                       |

|------|-------------------|--------------------------------------|---------------------------------------|

|      | mov               | al, cntctr2                          | - · · · -                             |

|      | @sout             | <crctr></crctr>                      | ; load count of                       |

| ctr2 | mov               | al, cntctr3                          |                                       |

|      | @_sout            | <pre><crctr></crctr></pre>           | ; load count of                       |

| ctr3 |                   |                                      |                                       |

| •    | hlt               |                                      | ; halt                                |

|      | inint :           |                                      |                                       |

|      | xor               | ax, ax                               | ; zero                                |

|      |                   |                                      | accumulator                           |

|      | xor               | cx, cx                               | ; zero reg. c                         |

|      | @_gin             | <intbuff></intbuff>                  | ; input interrup                      |

|      | ,                 |                                      | word                                  |

|      | cmp               | al, 01                               | ; check if 1                          |

|      | jnz               | intr21                               | ; if not 1 goto                       |

|      | @_gin             | <codbuff></codbuff>                  | intr21                                |

|      | @_gin             | <codbuff2></codbuff2>                |                                       |

|      | mov               | memsc, ax                            |                                       |

|      | @gin              | (                                    |                                       |

|      | @gin              | <codbuff4></codbuff4>                |                                       |

|      | mov               | memr, ax                             |                                       |

|      | mov               | ax, datlachclrnand                   |                                       |

|      | @_sout            | <li><lachclrnand></lachclrnand></li> |                                       |

|      | interint .        |                                      |                                       |

|      | integint :        |                                      |                                       |

|      | push              | ax                                   |                                       |

|      | mov               | ax, memsc                            |                                       |

|      | and               | ax, Ofh                              | ; extract it                          |

|      | add               | al, 01                               |                                       |

|      | mov               | cl, al                               |                                       |

|      | sh1               | ax, cl                               |                                       |

|      | sub               | ax, 01                               | ; decode count                        |

|      | @_sout            | <ctr1></ctr1>                        | from it                               |

|      | @_sout            | <ctr1></ctr1>                        | · · · · · · · · · · · · · · · · · · · |

| ctr1 |                   |                                      | ; output count to                     |

|      | рор               | ax                                   |                                       |

|      | mov               | ax, 1                                |                                       |

|      | mov               | c, ax                                |                                       |

|      | intret :          |                                      |                                       |

|      | iret              |                                      |                                       |

|      |                   |                                      |                                       |

|      | intr21:           |                                      | •                                     |

|      | mo∨               | ax, c                                |                                       |

|      | cmp               | ax, 1                                |                                       |

|      | jnz               | intr23                               |                                       |

|      |                   |                                      |                                       |

|      | mov               | ax, memrc                            |                                       |

|      | mo∨<br>and<br>cmp | ax, 7h<br>ax, 0                      |                                       |

|        | jnz<br>mov<br>@_sout<br>call<br>mov<br>mov<br>jmp        | chkbits<br>ax, datactand<br><actand><br/>near ptr modbuff<br/>ax, 2<br/>c, ax<br/>intret</actand> |

|--------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| intr1  | :<br>@gin<br>@gin<br>@gin<br>@gin<br>mov<br>mov<br>@sout | memmr, ax<br>ax, datlachclrnand                                                                   |

| integ  | int:                                                     |                                                                                                   |

| _      | mo∨<br>mo∨<br>mo∨<br>jmp                                 | ax, 1<br>c, ax<br>ax, 0<br>ini, ax<br>intret                                                      |

| intr22 | 2:                                                       |                                                                                                   |

|        | mov<br>cmp<br>jnz<br>mov<br>cmp<br>jnz<br>mov            | ax, c<br>ax, 2<br>intr23<br>ax, ini<br>ax, 1<br>theta<br>ax, 2<br>ini, ax                         |

| theta  | :                                                        |                                                                                                   |

|        | mov<br>@sout<br>mov<br>mov<br>jmp                        | ax, datintrand<br><intrand><br/>ax, 3<br/>c, ax<br/>intret</intrand>                              |

| intr23 | 3 :<br>mov<br>cmp<br>jz<br>mov<br>@_sout                 | ax, ini<br>ax, 2<br>intretrn<br>ax, datintrand<br><intrand></intrand>                             |

| intret | rn:                                                      |                                                                                                   |

|        | jmp                                                      | intret                                                                                            |

| chkbit | s:                                                       | •                                                                                                 |

|        | and                                                      | ax, 3                                                                                             |

|      |   | cmp<br>jnz<br>mo∨<br>mo∨<br>jmp | ax, 3<br>chk1<br>ax, 1<br>ini, ax<br>genrai |

|------|---|---------------------------------|---------------------------------------------|

| chk1 | : | and<br>cmp<br>jz                | ax, 1<br>ax, 1<br>genrai                    |

genrai :

,

| mov    | ax, datactand      |

|--------|--------------------|

| @_sout | <actand></actand>  |

| Call   | near ptr modbuffer |

| mov    | ax, datresand      |

| @_sout | <resand></resand>  |

| mo∨    | ax, 2              |

| mov    | i, 2               |

| jmp    | intret             |

modbuffer proc near

modb:

| mov    | · · ·                                 | nemsc |

|--------|---------------------------------------|-------|

| and    | ax, '                                 | 1070h |

| xor    | bx, b                                 | xc    |

| mov    | bh, a                                 | ah    |

| mo∨    | cl, (                                 | 55    |

| shr    |                                       | 51    |

| and    | ax, (                                 | 070H  |

| add    | ax, I                                 | x     |

| @_sout | <modb< td=""><td>uff&gt;</td></modb<> | uff>  |

| modbuffer | endp      |

|-----------|-----------|

| code_seg  | ends      |

|           | end start |

#### CREATE "MACRO.LIB"

; @\_sout

|       | macro<br>local | aport?<br>around, where |

|-------|----------------|-------------------------|

|       | push           | dx                      |

|       | out            | dx, al                  |

|       | mov            | where, dx               |

|       | jmp            | around                  |

| where | dw             | aport?                  |

around:

endm

| @_gin | macro | aport?        |

|-------|-------|---------------|

|       | local | around, where |

|       | push  | d×            |

|       | mo∨   | dx, where     |

|       | in    | al, dx        |

|       | jmp   | around        |

| where | dw    | aport?        |

around:

endm

#### CONCLUSION

In this project, a means of arriving at a previously hardwired circuit for a computer controller interface for a radio telescope correlator system has been attempted at, using an intelligent system based on a Intel 8088 microprocessor.

The existing system was made up of two boards VI A and VI B which were implemented using digital hardware only.

The system has the following advantages over the existing system.

a) The entire hardware is laid out on one card.

b) The system is easily software upgradable.

c) This system is perfectly compatible with the 80186 master processor of the data acquisition system.

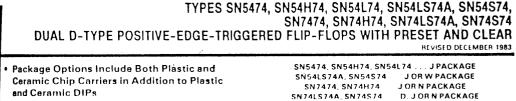

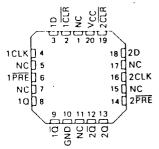

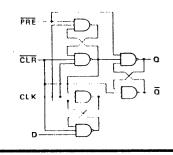

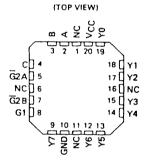

# DATA SHEETS

BIT - DEPT OF ELECTRONICS AND COMMUNICATION 1990 - 1991

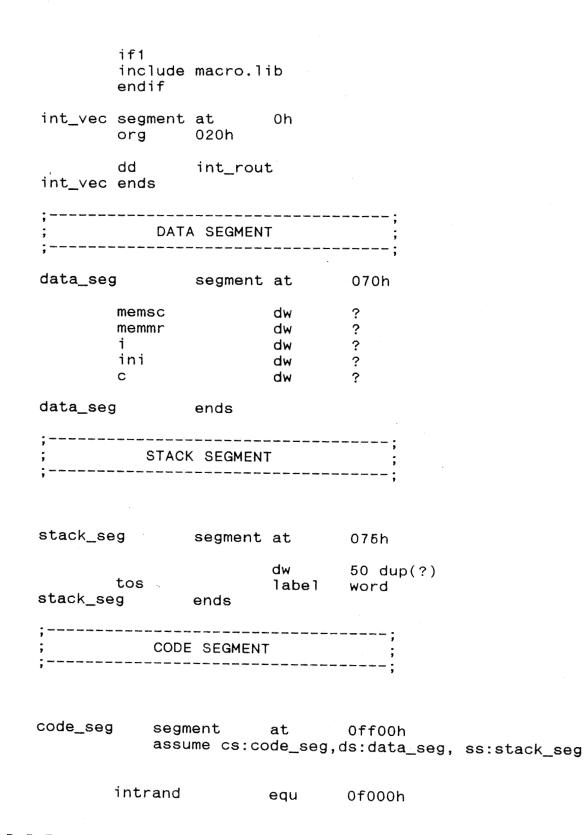

#### 8088 8-BIT HMOS MICROPROCESSOR 8088/8088-2

- 8-Bit Data Bus Interface

- 16-Bit Internal Architecture

- Direct Addressing Capability to 1 Mbyte of Memory

- Direct Software Compatibility with 8086 CPU

- 14-Word by 16-Bit Register Set with Symmetrical Operations

- 24 Operand Addressing Modes

- Byte, Word, and Block Operations

- 8-Bit and 16-Bit Signed and Unsigned Arithmetic in Binary or Decimal, Including Multiply and Divide

- Two Clock Rates:

--- 5 MHz for 8088

--- 8 MHz for 8088-2

- Available in EXPRESS

Standard Temperature Range

Extended Temperature Range

The Intel® 8088 is a high performance microprocessor implemented in N-channel, depletion load, silicon gate technology (HMOS), and packaged in a 40-pin CERDIP package. The processor has attributes of both 8- and 16-bit microprocessors. It is directly compatible with 8086 software and 8080/8085 hardware and peripherals.

à

#### Table 1. Pin Description

The following pin function descriptions are for 8088 systems in either minimum or maximum mode. The "local bus" in these descriptions is the direct multiplexed bus interface connection to the 8088 (without regard to additional bus buffers).

| Symbol                            | Pin No. | Туре | Nan                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ne and           | Function                                        |

|-----------------------------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------|

| AD7-AD0                           | 9–16    | 1/0  | ADDRESS DATA BUS: These lines constitute the time multiplexed<br>memory/IO address (T1) and data (T2, T3, Tw, T4) bus. These lines are<br>active HIGH and float to 3-state OFF during interrupt acknowledge and<br>local bus "hold acknowledge".                                                                                                                                                                                                         |                  |                                                 |

| A15-A8                            | 2-8, 39 | 0    | ADDRESS BUS: These lines provide address bits 8 through 15 for the entire bus cycle (T1-T4). These lines do not have to be latched by ALE to remain valid. A15-A8 are active HIGH and float to 3-state OFF during interrupt acknowledge and local bus "hold acknowledge".                                                                                                                                                                                |                  |                                                 |

| A19/S6, A18/S5,<br>A17/S4, A16/S3 | 35-38   | 0    | ADDRESS/STATUS: During T1, these are the four most significant –<br>address lines for memory operations. During I/O operations, these lines<br>are LOW. During memory and I/O operations, status information is<br>available on these lines during T2, T3, Tw, and T4. S6 is always low.<br>The status of the interrupt enable flag bit (S5) is updated at the<br>beginning of each clock cycle. S4 and S3 are encoded as shown.                         |                  |                                                 |

|                                   |         |      | used for data accessing.                                                                                                                                                                                                                                                                                                                                                                                                                                 | Ŭ                | ment register is presently being                |

|                                   | 1       |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  | ng local bus "hold acknowledge".                |

|                                   |         |      | S4                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <u>53</u>        | Characteristics                                 |

|                                   |         |      | 0 (LOW)<br>0<br>1 (HIGH)<br>1<br>S6 is 0 (LOW)                                                                                                                                                                                                                                                                                                                                                                                                           | 0<br>1<br>0<br>1 | Alternate Data<br>Stack<br>Code or None<br>Data |

| RD                                | 32      | 0    | <b>READ:</b> Read strobe indicates that the processor is performing a memory or I/O read cycle, depending on the state of the IO/M pin or S2. This signal is used to read devices which reside on the 8088 local bus. RD is active LOW during T2, T3 and Tw of any read cycle, and is guaranteed to remain HIGH in T2 until the 8088 local bus has floated.                                                                                              |                  |                                                 |

| READY                             | 22      | I    | This signal floats to 3-state OFF in "hold acknowledge".<br><b>READY:</b> is the acknowledgement from the addressed memory or I/O<br>device that it will complete the data transfer. The RDY signal from<br>memory or I/O is synchronized by the 8284 clock generator to form<br>READY. This signal is active HIGH. The 8088 READY input is not<br>synchronized. Correct operation is not guaranteed if the set up and hold<br>times are not met.        |                  |                                                 |

| INTR                              | 18      | 1    | INTERRUPT REQUEST: is a level triggered input which is sampled<br>during the last clock cycle of each instruction to determine if the<br>processor should enter into an interrupt acknowledge operation. A<br>subroutine is vectored to via an interrupt vector lookup table located in<br>system memory. It can be internally masked by software resetting the<br>interrupt enable bit. INTR is internally synchronized. This signal is active<br>HIGH. |                  |                                                 |

| TEST                              | 23      | 1    | TEST: input is examined by the "wait for test" instruction. If the TEST<br>input is LOW, execution continues, otherwise the processor waits in an<br>"idle" state. This input is synchronized internally during each clock<br>cycle on the leading edge of CLK.                                                                                                                                                                                          |                  |                                                 |

#### 8088

|                 | Table 1. Pin Description (Continued) |      |                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|-----------------|--------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol          | Pin No.                              | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| NMI             | 17                                   | I    | NON-MASKABLE INTERRUPT: is an edge triggered input which causes a type 2 interrupt. A subroutine is vectored to via an interrupt vector lookup table located in system memory. NMI is not maskable internally by software. A transition from a LOW to HIGH initiates the interrupt at the end of the current instruction. This input is internally synchronized. |  |  |  |

| RESET           | 21                                   | I    | RESET: causes the processor to immediately terminate its present activity.<br>The signal must be active HIGH for at least four clock cycles. It restarts<br>execution, as described in the instruction set description, when RESET<br>returns LOW. RESET is internally synchronized.                                                                             |  |  |  |

| CLK             | 19                                   | 1    | CLOCK: provides the basic timing for the processor and bus controller. It is asymmetric with a 33% duty cycle to provide optimized internal timing.                                                                                                                                                                                                              |  |  |  |

| V <sub>CC</sub> | 40                                   |      | $V_{CC}$ : is the +5V ±10% power supply pin.                                                                                                                                                                                                                                                                                                                     |  |  |  |

| GND             | 1, 20                                |      | GND: are the ground pins.                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| MN/MX           | 33                                   | 1    | MINIMUM/MAXIMUM: indicates what mode the processor is to operate in.<br>The two modes are discussed in the following sections.                                                                                                                                                                                                                                   |  |  |  |

The following pin function descriptions are for the 8088 minimum mode (i.e.,  $MN/\overline{MX} = V_{CC}$ ). Only the pin functions which are unique to minimum mode are described; all other pin functions are as described above.

| Symbol | Pin No. | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10/M   | 28      | 0    | STATUS LINE: is an inverted maximum mode $\overline{S2}$ . It is used to distinguish a memory access from an I/O access. IO/ $\overline{M}$ becomes valid in the T4 preceding a bus cycle and remains valid until the final T4 of the cycle (I/O = HIGH, M = LOW). IO/ $\overline{M}$ floats to 3-state OFF in local bus "hold acknowledge".                                                                                                   |

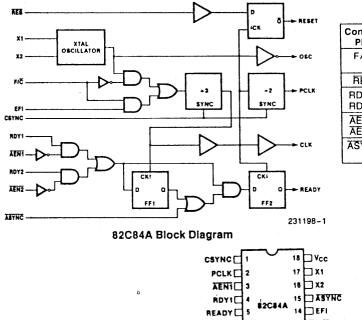

| WR     | 29      | 0    | WRITE: strobe indicates that the processor is performing a write memory or write $I/O$ cycle, depending on the state of the $IO/\overline{M}$ signal. WR is active for T2, T3, and Tw of any write cycle. It is active LOW, and floats to 3-state OFF in local bus "hold acknowledge".                                                                                                                                                         |