# MULTI-CHANNEL BUFFERED DATA ROUTER FOR A DIGITAL SPECTROMETER

## **PROJECT REPORT**

Jointly submitted in partial fulfilment of requirements

for the award of the degree of

# **Bachelor of Engineering in Electronics**

by

# SEETHA PRASAD M.G. SHRIKANTHA BHATTA .S

## UDAYA KUMAR B. VIVEK GARADY

UNDER THE GUIDANCE OF

#### Dr. T.S. RUKMINI RV College of Engineering

Bangalore

## Mr. A. SANTOSH KUMAR

Raman Research Institute Bangalore.

1994-95

#### DEPARTMENT OF ELECTRONICS

# **R V COLLEGE OF ENGINEERING**

BANGALORE

# BANGALORE UNIVERSITY R.V.COLLEGE OF ENGINEERING

BANGALORE - 560 059

Certificate

This is to certify that this project work entitled

# MULTI-CHANNEL BUFFERED DATA ROUTER FOR A DIGITAL SPECTROMETER

has been successfully carried out by

# SEETHA PRASAD M.G. UDAYA KUMAR .B SHRIKANTHA BHATTA .S VIVEK GARADY

in the partial fulfilment of the requirement for the

award of the Degree of

Bachelor of Engineering in Electronics

during the academic year 1994-95

Project Guide

Dr. T.S. RUKMINI

Prof. B.K. ANANTHA SWAMY

Dept. of Electronics Prof. B. K. Ananthaswamy Head of Department RV College of Engg. Dept. of Electronics Engg. Dept. of Electronics Engg.

R. V College of Engineering

#### RAMAN RESEARCH INSTITUTE

Certificate

This is to certify that the following Students have satisfactorily

completed the project entitled :

# MULTI-CHANNEL BUFFERED DATA ROUTER FOR A DIGITAL SPECTROMETER

was carried out at **RAMAN RESEARCH INSTITUTE** in partial fulfilment of the requirements for the award of "BACHELOR'S DEGREE in **Electronics Engineering** of Bangalore University during the year 1994-95.

VIVEK GARADY SEETHA PRASAD M.G. SHRIKANTHA BHATTA S.

UDAYA KUMAR B.

Enthop Kumar. A. Mr. A. Santhosh Kumar

Electronics Engineer

Address : C V Raman Avenue Sadashivanagar Bangalore 560 080, India

Tel: (080) 334 0122 Fax: (080) 334 0492 Telex : 845 2671 RRI IN Telegrams : RAMANINST email : root@rri.ernet.in

a . •

## ACKNOWLEDGMENTS

We are obliged to our professor and Head of the department of electronics engineering **Prof. B.K Anathaswamy** for the encouragement and help he has given us.

We are grateful to the **Director**, **Raman research Institute**, and **Dr. K R Anantharamaiah** for having given us an opportunity to undertake our project work in this reputed institute.

We are highly indebted to our guide Mr. A. Santhosh Kumar, who has motivated and guided us and has been a source of inspiration throughout our project work.

We wish to express gratitude to **Dr. T.S Rukmini**, department of Electronics, R V College of Engineering, for her guidance and support during the course of our project.

We would like to thank Mr. H.N. Nagaraj for his invaluable help in the design of PCB's.

We would like to express our gratitude to field staff in Gauribidanur for cooperating with us during our stay there.

Last but not the least we wish to acknowledge the co-operation provided to us by all the staff members of the Electronics Lab and GMRT lab during the course of our project.

> Vivek Garady Seethaprasad M G Shrikantha Bhatta S Udaya Kumar B

## **CONTENTS**

#### **PROJECT SYNOPSIS**

#### CHAPTER 1.

#### **PROJECT OVERVIEW**

- 1.1 INTRODUCTION

- 1.2 MULTI CHANNEL SPECTROMETER

#### CHAPTER 2.

#### **DESIGN PHILOSOPHY**

- 2.1 THE PROBLEM

- 2.2 DESIGN PRINCIPLE OF DIGITIZER CARD.

- 2.3 DESIGN PRINCIPLE OF BUFFERED DATA ROUTER.

#### CHAPTER 3.

#### HARDWARE IMPLEMENTATION

- 3.1 DIGITIZER CARD IMPLEMENTATION.

- 3.2 BUFFERED DATA ROUTER.

- 3.2-1 SEQUENCER CIRCUIT.

- 3.3 CLOCK CONTRIOL CIIRCUIT.

#### CHAPTER 4.

#### TESTING AND CONCLUSION.

4.1 TESTING OF DIGITAL CONTROL LOGIC.

## APPENDICES

#### APPENDIX - A

#### GAURIBIDANUR RADIO TELESCOPE (GEETEE)

T

APPENDIX - B

#### CARBON RADIO RECOMBINATIONS LINES (CRRLS)

APPENDIX - C

MAX-PLUS AND EPLDS.

#### APPENDIX - D

DATA SHEETS.

## **PROJECT SYNOPSIS**

#### **Introduction:**

We are involved in designing and implementing a programmable High speed Multi Channel Data Acquistion cum Signal Processing System. The *Buffered Data Router* is going to the front end of the Fast Fourier Transform card (FFT) which forms the kernel of a digital spectrometer.

The FFT card was designed at RRI. At the heart of the FFT card lies a Fast Fourier Transform Processor the PDSP16150 from PLESSEY SEMICONDUCTORS. This digital spectrometer (including our BDR) will be assimilated into the Gauribidanur radio telescope, and will be used to study carbon radio recombination lines.

#### **Functional explanation:**

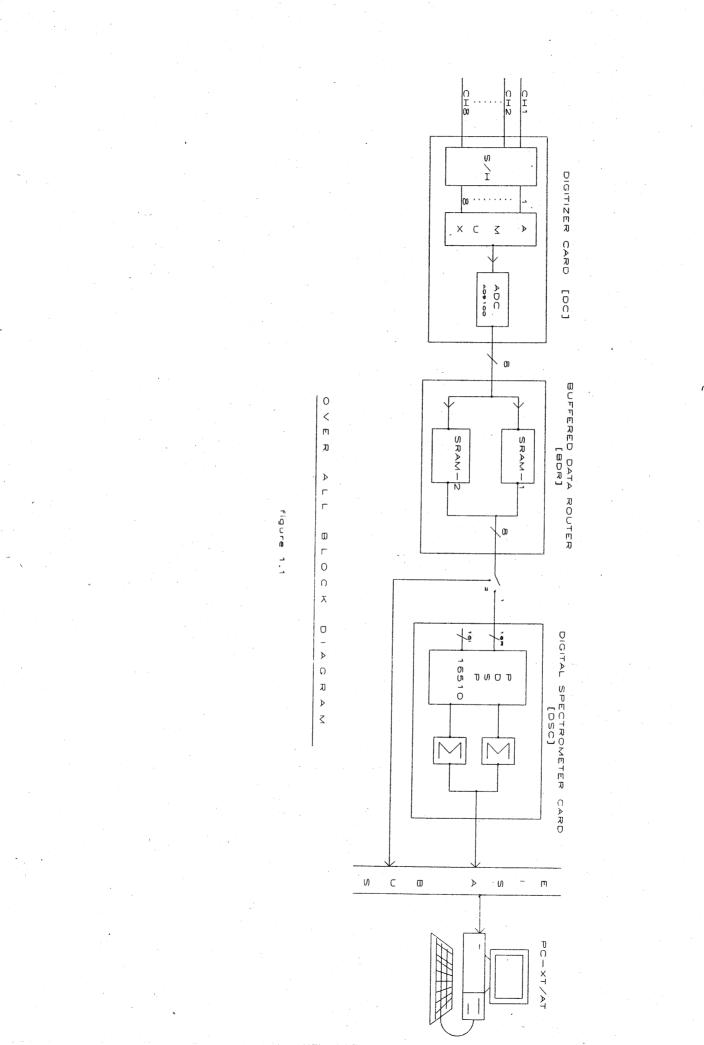

The block diagram shows the overall Multi-Channel Digital Spectrometer hardware. The BDR is at the top of the hiearchy as far as data flow is concerned. The signals in analog domain are digitized and stored in memeory banks in BDR module itself. It is then furnished to the FFT module in contigious blocks.

The FFT module consists of the FFT chip which accepts data on two 16-bit input channels either as real or imaginary parts of a complex sequence or as two independent sequences. This chip then compiles the fast fourier transform of the input data at very high speed. The output is also in the form of 16-bit integers. This output is fed to an integrator, where the fourier samples, are integrated in order to extract the signal buried in noise. The pipelined adders required for integration are incorporated in high density EPLDs called FLEX devices.

A PC/AT based interface has been developed for high speed acquistion of data and then transfered directly on the hard disk, at speeds of a few Mbytes per second. This interface is designed to follow **Extended Industry Standard Architecture (EISA)** bus standards, which allows 32-bit transfers.

#### **Design of BDR:**

The system is to be designed in such a way that it can acquire signal both in the time domain and in the frequency domain. To accomplish this, we intend to design the system around high speed ADCs, Multiplexers etc.

The design of the high speed BDR is still under scrutiny for the following reasons. We have two design philophies in mind, they are:

- (a) To use only a single ultra high speed ADC with a analog multiplexer preceeding it.

- (b) To use eight medium speed low cost ADCs

Is it feasible to use a single ultra high speed ADC operating at several megacycles per second with all the associated circuitry to compensate high

frequency errors or use eight ADCsfor the eight channels, operating at several kilocycles per second?

It is a problem of optimization of cost, performance and circuit simplicity.

Our BDR is programmable, in the sense that, the user can opt the number of channels (1to 8) and select the number of points for the FFT computation. The various modes of operation and the data rate can be 16 point complex at 24 Msamples/sec or 2\*1024 point complex at 12Msamples/sec and so on.

We have to design the base band filters as depicted and a EISA interface for FFT card.

The BDR is going to have as a wide range of applications. Due to its programmable flexibility it can be used in a multitude of situations where the number of channels required vary. With just the EISA interface (excluding FFT card) the system can also perform as a high speed DAS. It can also be used as a general lab spectrum analyser. The design of the BDR is such that, in future when ultra high speed ADCs are available at low costs they can be swapped with the existing ones with rest of the circuitry unchanged.

# CHAPTER ONE PROJECT OVERVIEW

**B. E.** (E & C) Final Year Project 1994–95 Bangalore University

### 1.1 INTRODUCTION.

Fourier Transform(FT) is fundamental tool of spectrum analysis used in several applications, both commercial and scientific. Among its applications in Radio Astronomy, there is an ever-growing need for faster computation of FT over long sequences of data samples. Conventionally, this is realized with highly optimized, "fast" fourier transform algorithms written on high speed, general purpose computer system. In such a case, the cost to computation ratio for a general computer proves too very uneconomical. In several cases, it may be required to obtain spectra of signals in real-time, before recording. However there are many applications demanding a throughput rate that cannot be afforded by these computers and quite often, one needs a dedicated FT processor.

In real time applications, these devices may be used as embedded processors in the target circuits and can as well be interfaced suitably to work as "accelerators" for general purpose computers. Engineers at RRI have developed a flexible Digital Spectrometer Card(DSC) to function for both of these purposes.

The genesis of this design is a part of an ongoing Pulsar instrumentation work. Apart from observation of pulsars, the system can be used in a variety of astronomical applications like the Radio Recombinational lines studies, Electron Proton Annihilation studies, or as a general purpose Spectrometer which can perform long stretches of integrations

### **B. E.** (E & C) Final Year Project 1994–95 Bangalore University

#### **1.2 MULTI - CHANNEL SPECTROMETER**

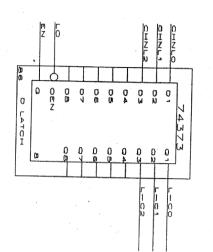

At the heart of the SPECTROMETER is a DSP chip PDSP16510. This is a dedicated FFT chip. This chip accepts data on two 16-bit input channels, either as the real and imaginary parts of a complex sequence, or as two independent real sequences. It can perform FFT over different lengths of data sequence, for example- 16, 64, 256 & 1024 points at the maximum rate of 12 M samples/sec. This output can be either acquired by a PC/AT with EISA BUS interface or can be integrated in the buffers of the DSC. The integration buffers are implemented by using FIFOs as the associated control logic will be bare minimum. The user can integrate the data up to 2<sup>16</sup> times in these buffers. When integrated, data can be written on to the hard disk. At the same time the integrated fourier transformed output will be written into the other FIFO and this process repeats.

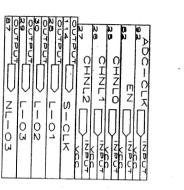

The DSC does not include the necessary interface circuitry for interfacing the signals from the Real world domain to the Digital Domain. Being single channel spectrometer, it offers limited resolution. In order to develop a completely independent, multi-channel Digital Spectrometer, we have designed a programmable 8-channel Digitizer card and a Buffered Data Router(BDR). The over all block diagram of the system is shown in fig(1.1)

The programmable 8 channel Digitizer Card has a bank of 8 sample and hold circuits at the front end, for sampling the analog signals. It is followed by 8x1 analog multiplexer whose

ing sai Baint

#### **B. E.** (E & C) Final Year Project 1994–95

Bangalore University

output is fed to a 10-bit ADC. This ADC is of FLASH type which can work at a maximum speed of 18 Msamples/sec and has a novel pipelined architecture. Due to its piplined architecture, after 4 clock cycles the digitized data flows out continuously. The start of conversion and end of conversion pulses are not necessary to digitize each sample, thus simplifying the control circuitry. The digitized data is then fed to the Buffered Data Router [BDR].

The BDR is equipped with a double buffer of SRAM memory chips and the necessary control logic. Input data is first written into BUFFER-A at the rate programmed by the user depending upon the input bandwidth. As soon as the programmed number of points per channel have been written, the address counter sends a buffer full signal to the MUX circuits. At this point the MUX swaps the buffers. The input data is now written into BUFFER-B while BUFFER-A will be read by host CPU or the DSC. The buffers are swapped again when BUFFER-B sends its buffer full signal to the MUX circuits, and this process repeats.

The ALTERA programmable logic development system was used to integrate various logic circuits into MAX-7000 and MAX-5000 family EPLDs. In fact we have used EPM7128LC84 (84-pin EPLD), which appertains to the MAX-7000 family while the other is EPM5016 (20-pin EPLD) of MAX-5000 family. These chips provide a comprehensive costeffective solution for designs, intensive in combinatorial logic.

# CHAPTER TWO DESIGN PHILOSOPHY

**B. E.** (E & C) Final Year Project 1994–95 Bangalore University

#### 2.1 <u>THE PROBLEM.</u>

The crux of the problem lies in radio observations of low frequency Carbon Radio Recombination Lines (CRRLs) by making use of the Multi Channel Spectrometer. By "Lines" we ascribe to radiation at unique wavelengths. Every element has a unique emission spectrum - finger prints of elements. These lines are caused for the following reason. When an electron is excited by supplement of energy either thermal or non-thermal, the electrons move to an higher energy level (orbit). This state is quasi-stable state, hence it falls back to its previous stable state, i.e. lower energy level. In doing so the difference in energy is radiated as electromagnetic radiation. Since energy levels are quantized, the emitted energy is of definite wavelength.

At the Gauribidanur Radio Telescope (GEETEE) [ please refer to Appendix-A.] the recombination lines can be observed at decametric wavelengths. The operating frequency of the GEETEE is 34.5 MHz, with a good usable bandwidth of 2 MHz. The CRRLs at these frequencies correspond to high principal quantum numbers around 574 $\alpha$ , with typical line widths of the order of 1kHz. Within the observational bandwidth of GEETEE 12 of these CRRLs can be observed [please refer to Appendix-B]. In order to observe these lines a

### **B. E.** (E & C) Final Year Project 1994–95 Bangalore University

resolution of approximately 250 Hz is an essential condition. Hence it was conceived to build a stable Spectrometer, which could be used for the above said observations.

The DSC could not be used in its present form of single channel spectrometer, because of the poor resolution that could be obtained, which is elucidated in the following discussion.

The resolution of the Spectrometer is defined as:

Resolution = BW / N Hz.

where BW is the Bandwidth and N is the number of points of FFT performed.

If we determine the resolution of the Spectrometer for 2 MHz bandwidth with 1024 points FFT it turns out to be :

#### Resolution = 2 MHz / 1024 = 1953.12500 Hz

The resolution obtained is clearly inadequate for useful observations. In order to improve the resolution, we have hit upon the novel idea of splitting the 2 MHz bandwidth into 8 separate bands each of bandwidth 250 kHz and then performing a 1024 point FFT on each of them. This will improve the Resolution, by a factor of 8 and the resolution would now be

#### Resolution = 250 kHz / 1024 = 244.140625 Hz

which could be used conveniently for the observations.

Ο Ш N ----ດ Ζ 0 U Ч \_ 0

Ζ Ŋ

figure 2.1

DESIGN (b)

#### 2.2 DESIGN PRINCIPLE OF DIGITIZER CARD.

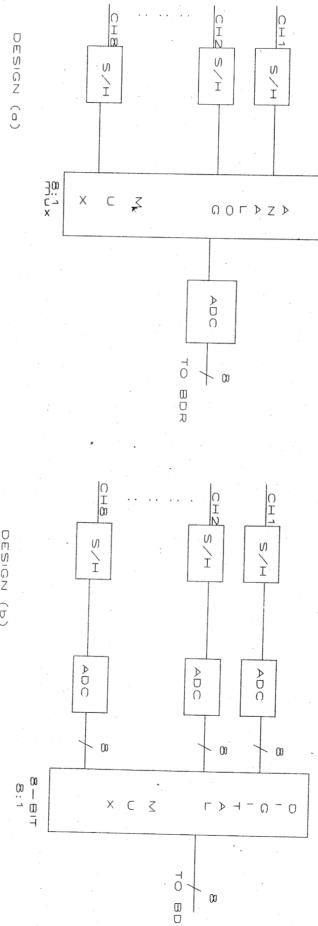

The design dogma is now dictated by the *reductio ad absurdum* in the previous section. It is now clear that the number of input channels for BDR is 8. There are two design philosophies which can be implemented.

They are:

(a) To use a single high speed ADC with a analog multiplxer.

(b) To use eight medium speed ADCs with a digital multiplxer.

The block diagram of the two designs are shown in fig(2.1). Comparing the two design philosophies, we will come to know that design (a) is cost effective and simple in terms of circuitry. The reasons are obvious, when one looks at the two designs. The first point we notice is that we need 8 ADCs for design (b) while only one ADC is sufficient for design (a). Since the ADCs are of 8-bit resolution we need a 8-bit 8:1 Digital Multiplexer for design (b). The Digital Multiplexer may not be available or may be too expensive. All these bottle necks are not encountered in design (a).

#### 2.3 DESIGN PRINCIPLE OF BUFFERED DATA ROUTER.

The BDR furnishes digitized data to the DSC card. It should take heed of supplying data in proper format and at required throughput rates so that both of them work in synchronism.

When we give a "Sample" command to the S/H circuit we are actually sampling 8 input analog signals appearing at 8 input channels. After digitizing we obtain a serial output of 8 data points, each of which corresponds to 8 channels in sequential order. It is quite evident that we cannot send these data words directly to DSC, because individual data points do not have any correlation with each other as they are from different channels. There is one way out of this bottle neck, that is by storing the data temporarily on some storage device and then throughputting the data in contiguous blocks to the PDSP chip. Therefore we are making use of a memory (SRAM) as temporary storage.

After 1024 data points from each channel has been written, it is read out of the memory in the fashion the PDSP desires. Subsequently we will be storing a maximum of 8 \* 1024 = 8192 data points. Inevitably we need a 8K RAM chip to accommodate this data.

Continuum supply of data necessitates read and write simultaneously Since this is not possible on a RAM chip, we are left with a choice of using two 8K RAM chips(of course, we

## **B. E.** (E & C) Final Year Project 1994-95 Bangalore University

could use Dual-Port RAM, but the control circuitry would be involving and complex) hence we restrain ourselves to a simple design involving two RAMs. We apportion 1K in both of the 8K RAM chips for each channel. Individual data points are written in their respective 1K blocks. After 8192 samples and digitization we are left with one of the RAM chips full of data where in, each 1K block of memory corresponds to one particular channel. Now we can read out of RAM chip and furnish this data to DSP. Simultaneously we can continue to write fresh data into the second RAM chip. Under this circumstance the PDSP chip sees a continuous stream of data from BDR even though the acquisition is by fits and starts.

# CHAPTER THREE HARDWARE IMPLEMENTATION

**B. E.** (E & C) Final Year Project 1994–95 Bangalore University

### **3.1 DIGITIZER CARD IMPLEMENTATION**

With the design of digitizer card finalized, it can be seen that it will require these basic components:

- Sample and Hold circuits

- Analog Multiplexer

- Analog to Digital Converter

#### Sample and Hold circuit:

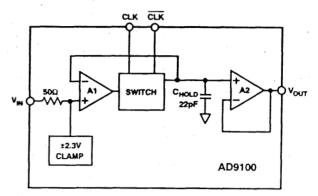

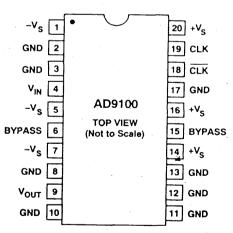

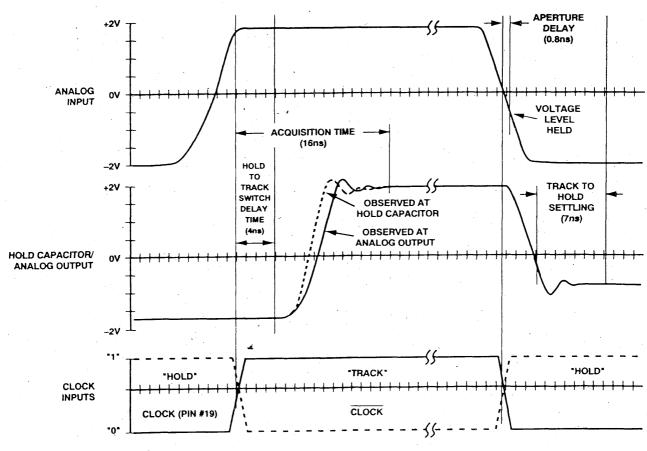

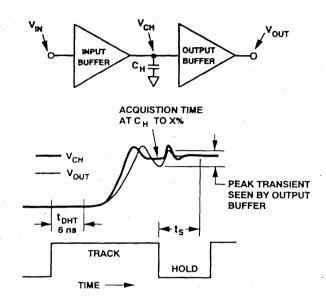

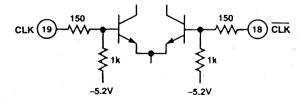

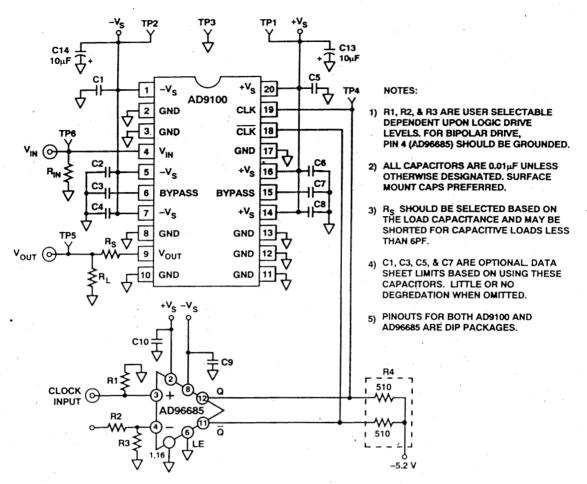

The signals from all the 8 channels are sampled at the same instant of time. The S/H circuits will be holding the same analog value till the next sample pulse is applied. With an input frequency band of 250 kHz, the Nyquist sampling frequency will be 500 kHz. So the time interval between two samples is 2µsecs. In this time period the ADC will have to digitize all 8 channel outputs starting from the first channel through the last channel in sequential order. Hence there will be 0.25µseconds for each channel to be digitized. The S/H on the 8th channel will therefore, have to hold its output for 1.75µseconds. We have chosen *AD9100* for sampling the analog signals, which has a typical droop rate of 1mV/µs. The droop in output voltage of the last S/H is 1.75mV. The resolution of the ADC used (AD773) is 0.97mV. So a change of 1.75mV at the S/H output will lead to an approximate change of 2 bits in the digitized value of the ADC output. This

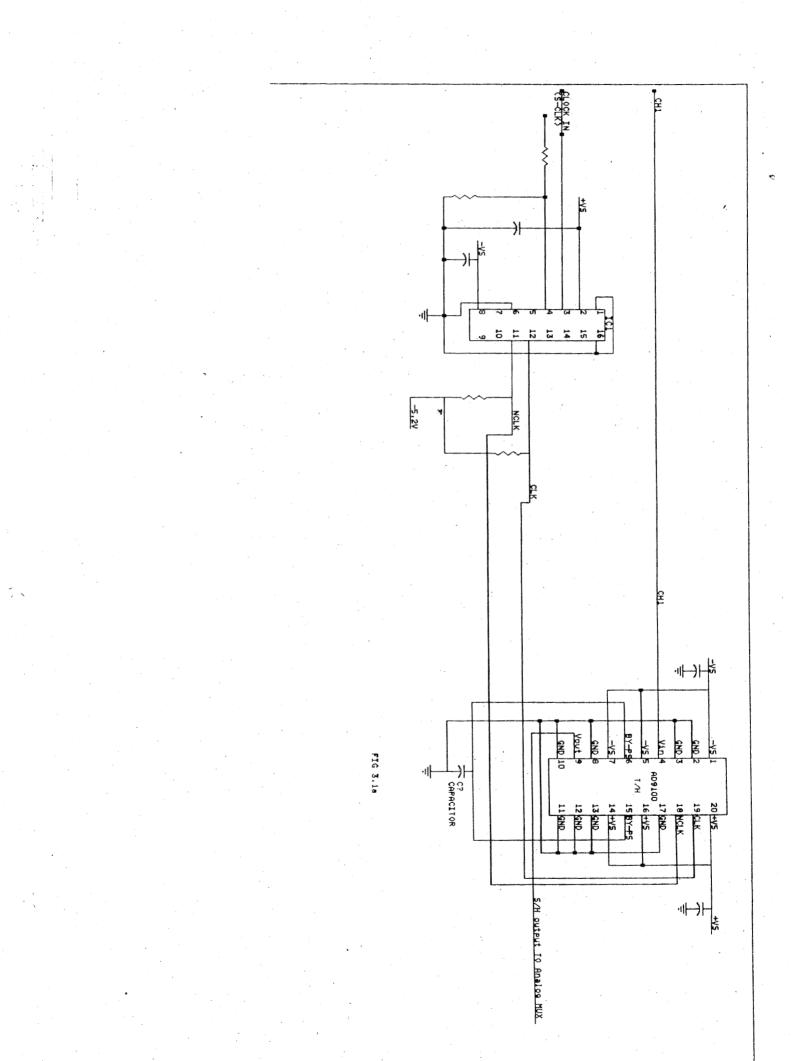

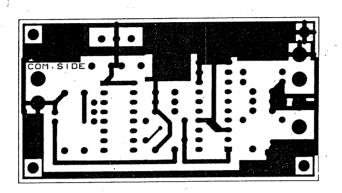

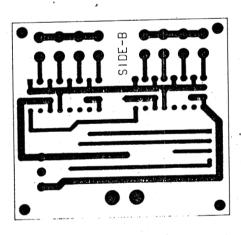

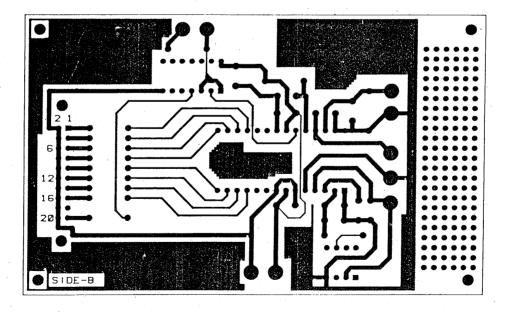

# PCB Layout of S/H Circuit Fig 3.1

#### **B. E.** (E & C) Final Year Project 1994–95

#### Bangalore University

kind of accuracy is acceptable for all practical purposes. The schematic and the PCB layout of the S/H circuit is as shown in the fig (3.1a & b). Further details of the S/H AD9100 can be found in Appendix D.

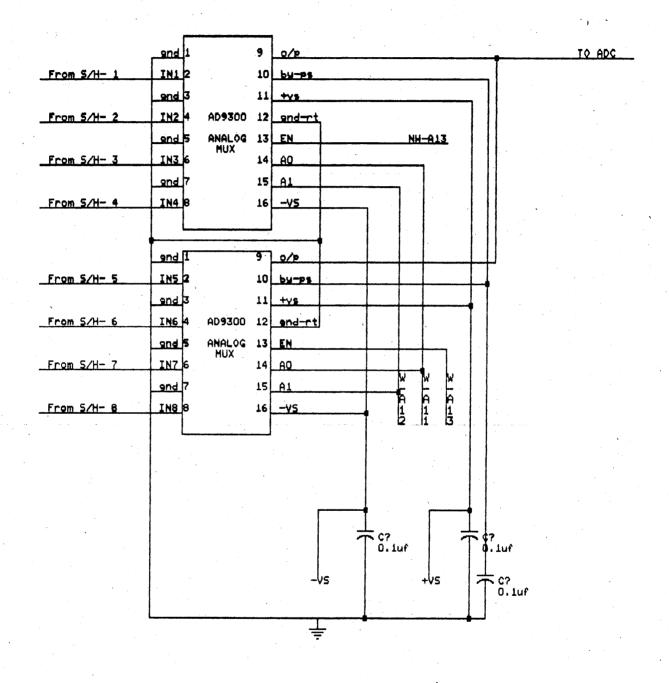

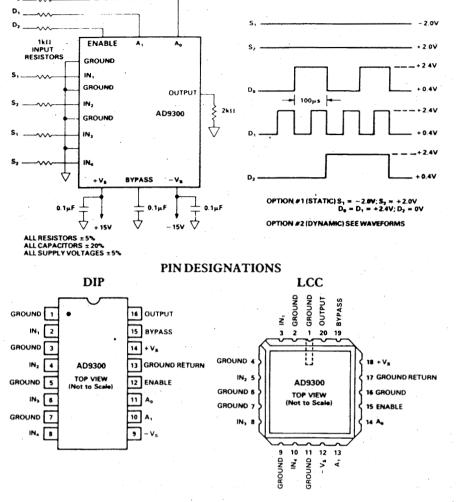

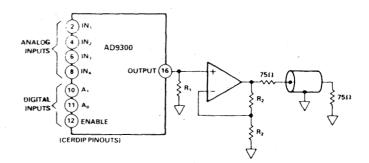

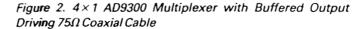

#### **Analog Multiplexer:**

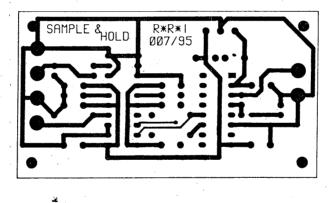

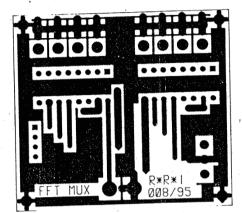

The Analog MUX will have to switch all the eight outputs of the S/H circuits to the ADC for digitizing before the arrival of the next sample pulse. This gives it an interval of 0.25 $\mu$ seconds to switch between two channels. This time should include all the delays involved in a MUX, like settling time and channel has a settling time of 70ns (typical), and channel switching time of 40ns (typical). The AD9300 is a 4:1 multiplexer. However, its output can be put into high impedance state. This will allow us to use two such MUXes in parallel, forming a 8:1 multiplexer. The schematic and PCB layout of the MUX are shown in *fig(3.2a & b)*. Further details of the MUX can be found in *Appendix D*.

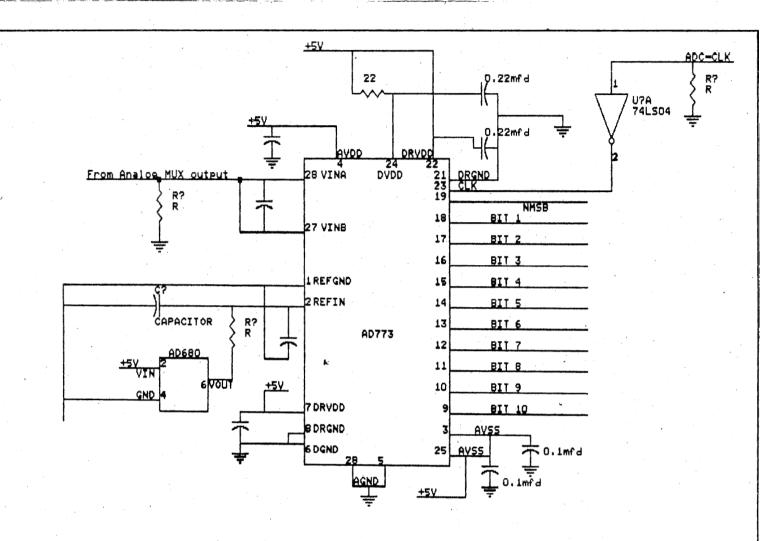

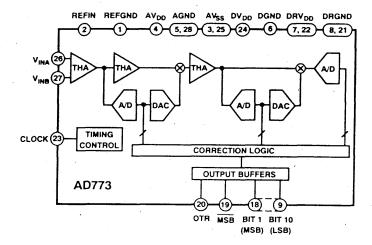

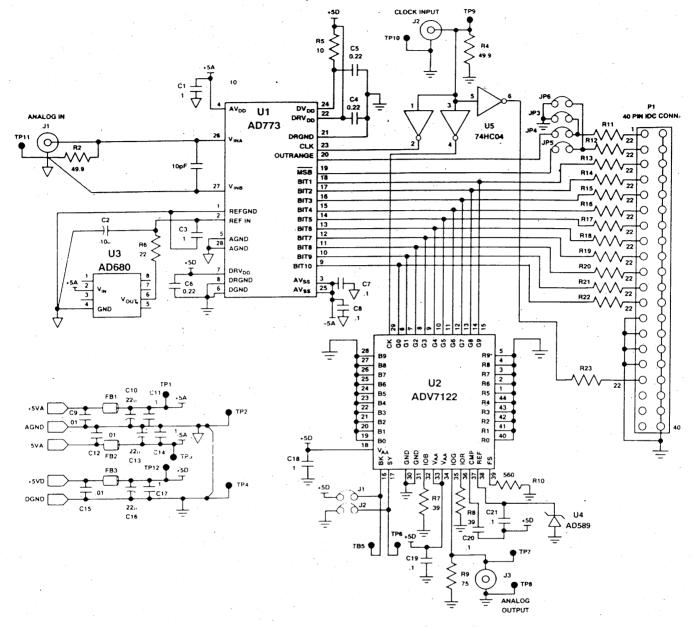

#### Analog to Digital converter:

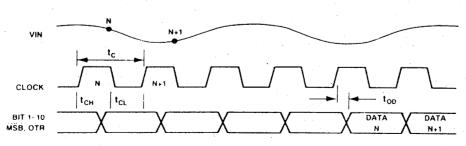

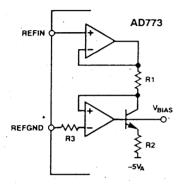

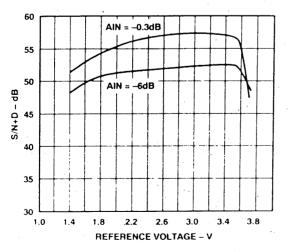

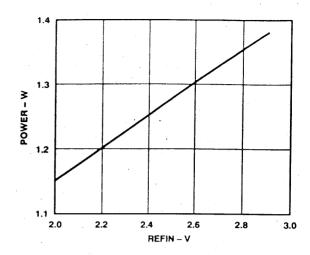

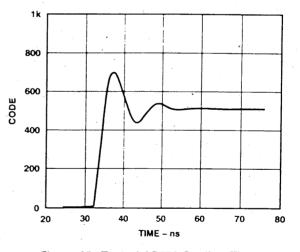

After the sample pulse is given to the S/H circuits the Analog to Digital converter will have to digitize the outputs of all the 8 channels. So the ADC will have to operate at eight times the speed of the S/H circuits. With a sampling frequency of 500 kHz given to the S/H circuits, the ADC has to therefore, operate at 4 MHz, giving the ADC a conversion time of 0.25µseconds. With this factor in view the ADC we selected was *AD773*. It is a monolithic 10-bit, flash ADC, with a throughput rate of 18 MSPS ADC with a on board track and hold Dept. of E & C Engineering, **R.V.C.E.** Bangalore

FIG 3.2a

PCB Layout of Analog MUX Circuit

Fig 3.2

**B. E.** (E & C) Final Year Project 1994–95 Bangalore University

amplifier. AD773 is a pipe lined device. It has a delay of four clock pulses between an analog voltage applied at its input and the corresponding digitized data appearing at its output. It has an input range of 1V (peak-to-peak). Since the resolution of a ADC is given by:

#### Resolution = input voltage swing $/(2^n)$ ;

where n is the number of bits of ADC output.

This gives a resolution of (1V/(1024))

Resolution = 977.4  $\mu$ V.

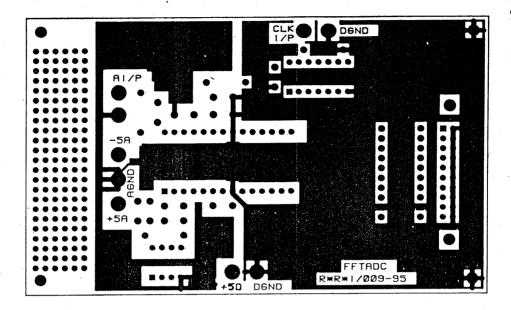

With a conversion time of  $5.55 \times 10^{-08}$ , this ADC is ideally suited for specifications imposed by the Digitizer card. The schematic of the ADC and it's PCB layout is shown in *fig* (3.3a & b). Further details regarding AD773 can be obtained in *Appendix D*.

| Size Doc  | ument Number    | i   | REV |

|-----------|-----------------|-----|-----|

| A         |                 |     |     |

| <br>Date: | July 8, 1995 Sh | ret | of  |

PCB Layout of ADC Circuit

Fig 3.3

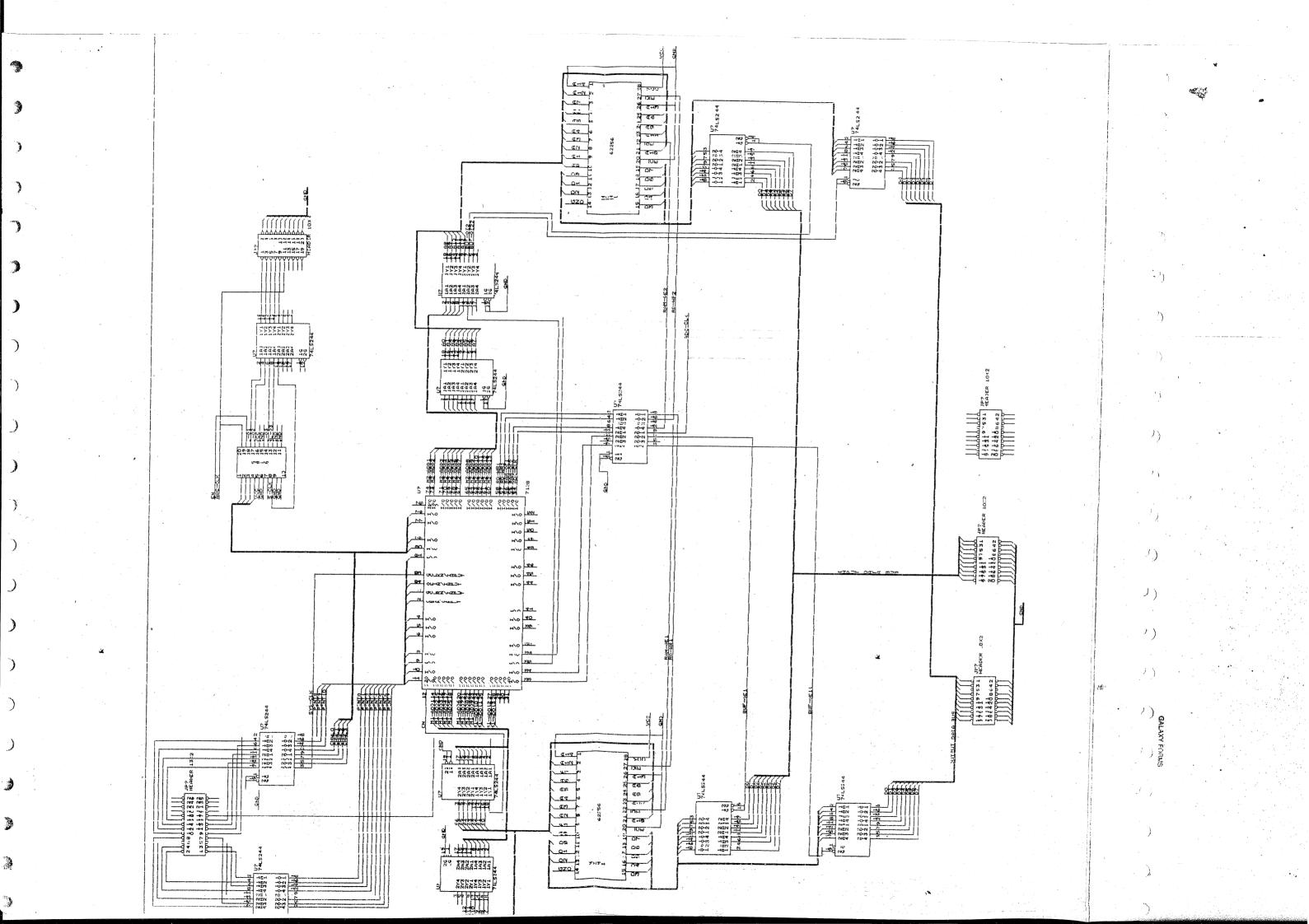

# B. E. (E & C) Final Year Project 1994–95 Bangalore University 3.2 <u>BUFFERED DATA ROUTER</u>

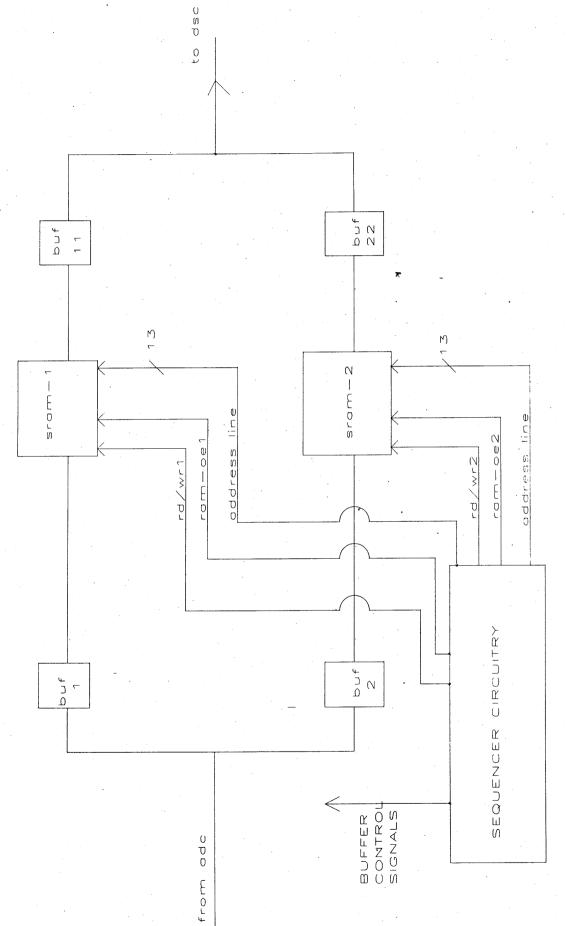

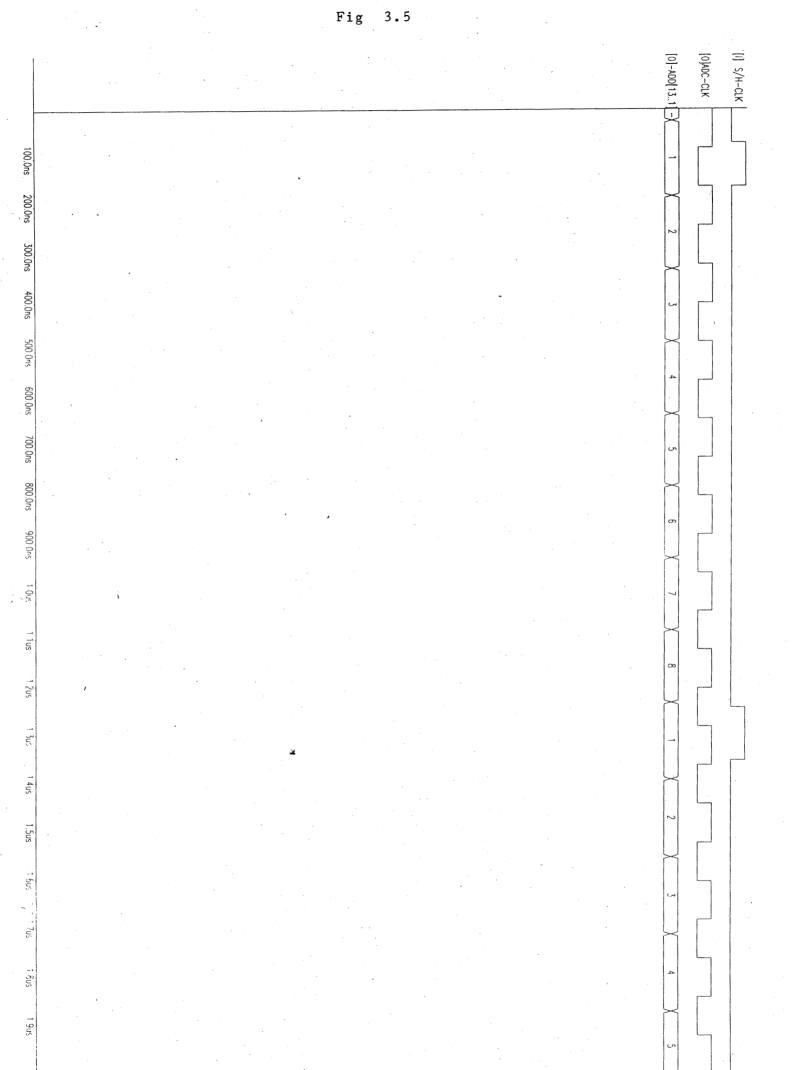

Spectrometric analysis of the signals received from the radio telescope is continuous process. This involves a continuous flow of data through the **Buffered Data Router** (fig(3.4)), to the FFT card. With 8 different channels involved, a rearrangement of digitized ADC output is needed. This is because the FFT chip requires the entire set of 1024 (or 512 or 256 ...) points of a single channel, given to it consecutively. But the ADC will be digitizing the signals of all the channels' one after another. So if at the n<sup>th</sup> clock pulse, the digital output from ADC is from channel x (say), then at the (n+1)th clock pulse the digital output is from (x+1)th channel. If the ADC output was to be given directly to the FFT card, two consecutive data outputs from the ADC will be from two entirely different channels as shown in *fig (3.5)*. Processing of such a stream of data would lead to faulty results in the FFT output.

To sort out this problem, rearrangement of the ADC output must be performed. This task involves temporary storage of digitized data on the *BDR*. RAMs are best suited for the job of temporary storage, when the required speed of operation and cost are taken into perspective. With the requirement of 1024 points FFT on all 8 channels, the total amount of data to be stored will be 8192 bytes, with 1kB for each channel. Data from a channel will be written into its corresponding 1kB block, after being digitized by the ADC. This stored data is then read in a stream of 1024 data points from the same channel.

To keep the data flowing ceaselessly, it must be read from and written into the RAMs simultaneously. But RAMs present a problem. At a given instant of time, they can perform

Ю 10 4.

.

only one task, either reading or writing. Both these operations cannot be performed simultaneously. This predicament is preempted by using two separate memories. While one of them is storing data from the ADC, the other will be sending previously stored data down to the FFT card after the required rearrangement.

To perform this prestidigitation of writing and reading data simultaneously into the respective memories and then swapping the operation, the *Buffered Data Router* has been used.

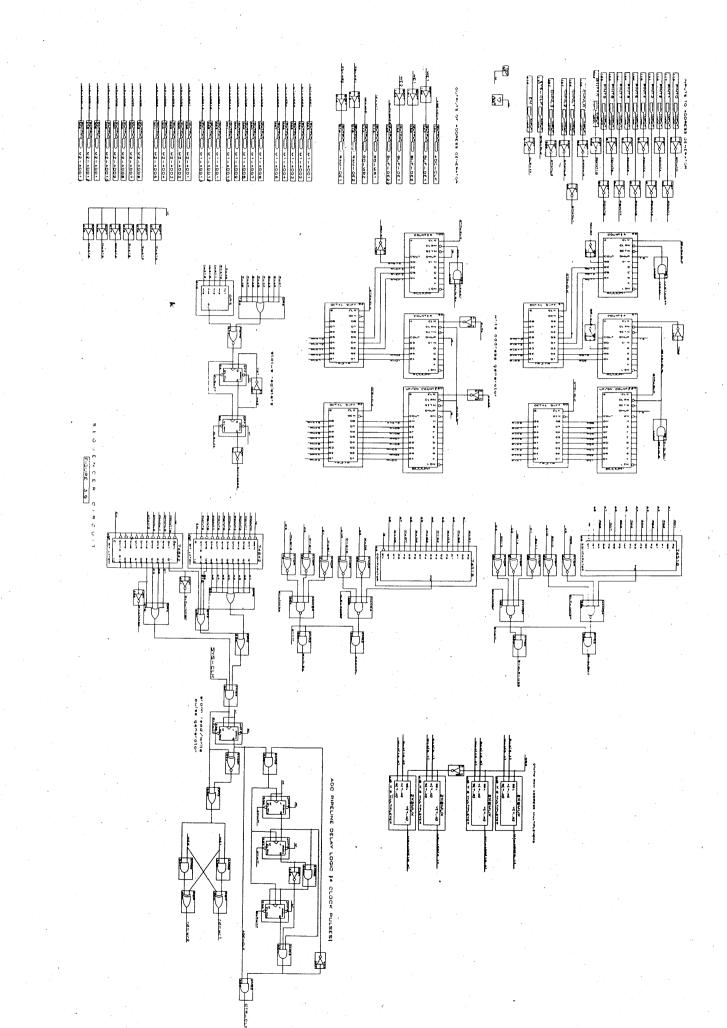

The BDR consists of the following blocks:

(a) Sequencer Circuit

(b) Memory banks.

#### 3.2-1 SEQUENCER CIRCUIT:

The sequencer circuit forms the quintessence of the *Buffered Data Router*. It functions as an address generator for the two memories and also for controlling the read and write operations of static RAMs. The ability to program the number of points and channels involved in the FFT process, is one of the feature incorporated into the *BDR*. This means the user will stipulate the number of points and channels. This is a vital information for the sequencer circuitry.

## B.E. (E & C) Final Year Project 1994-95

### Bangalore University

The inputs to the sequencer circuit are as follows:

- •number of points

- •number of channels

- •clock

- •enable signal

The stipulated number of channels and points are accepted from the user by means of a program written in C language. Using either an ISA or EISA interface card, this information is then fed to the *BDR*. The sequencer circuit in the *BDR* accepts this data and stores it in the appropriate latches.

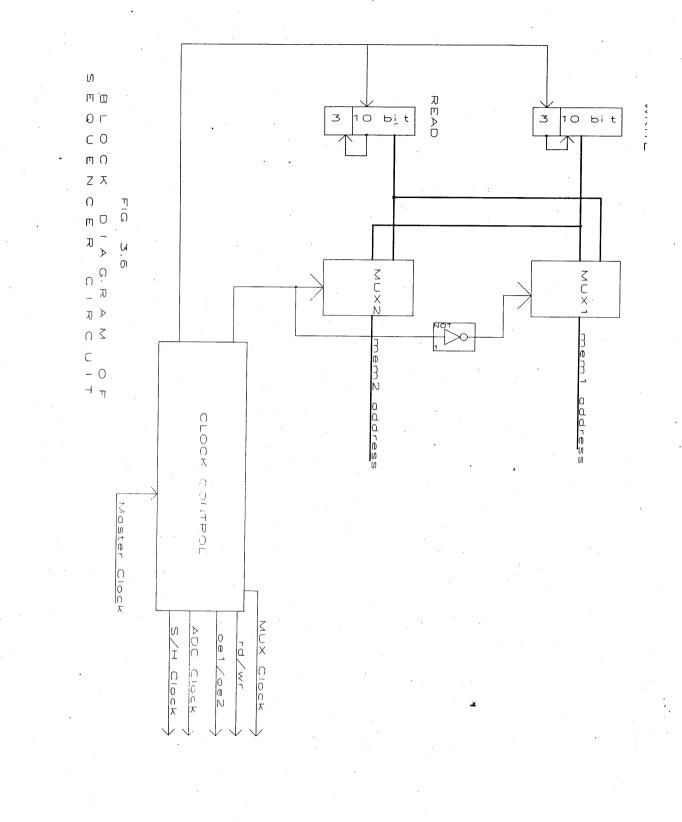

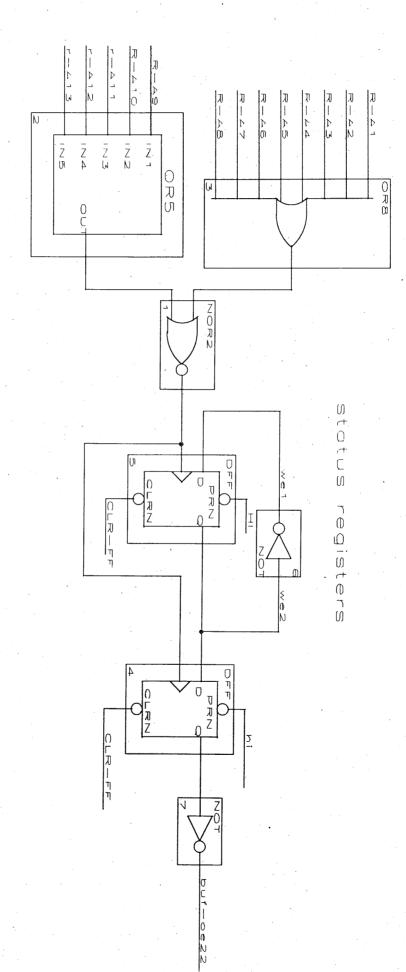

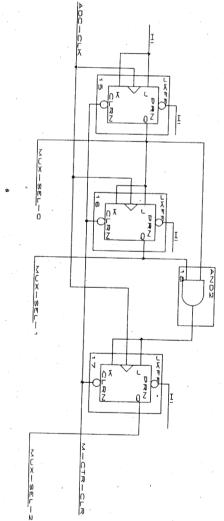

The block diagram of the sequencer circuit is as shown in fig(3.6). The sequencer circuit itself can be categorized as:

- a) Address Generator and Multiplexer

- b) Clock Controller

#### **ADDRESS GENERATOR:**

The address generator is used for generating address sequence for read and operations performed on the two memories. In order to access all 8k locations in the S-RAMs, a 13 bit address is required. This 13 bit address is generated by a 13 bit counter. With reading and writing address taking place simultaneously two address generators are required, namely, the read address generator and write address generator.

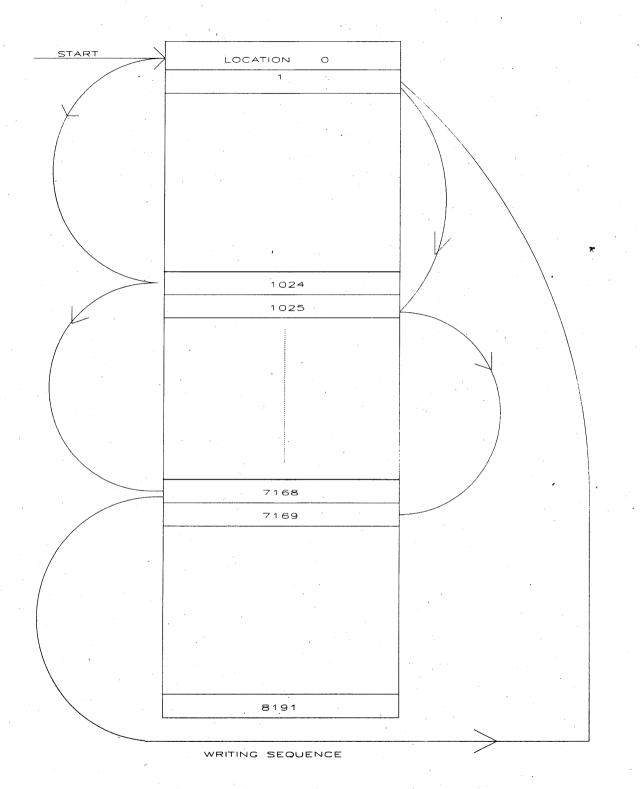

### (a) Write Address Generator:

As explained earlier, the memory is divided into eight 1 kB blocks and each 1k block is for holding data from one channel. Two consecutive outputs of ADCs are from two different channels. They need to be stored into their respective 1k blocks. Therefore at every clock pulse the write address generator has to increment itself by 1024 in order to point to the correct memory block. After storing data points from all N<sub>c</sub> channels it will have to switch to switch to first 1k block and point to next free location in it. The sequence of write address generated is shown in fig(3.7)

To achieve this the write address generator is divided into 2 parts a 3 bit counter and a 10 bit counter. Both these counters are programmable. The number of points are programmed into the 10 bit counter and the number of channels are programmed into the 3 bit counter. The 3 bit counter is clocked by the master clock. At every clock pulse, it's incremented by one. The significance of this 3 bit counter, is that the 13 bit address is incremented by 1024 at every clock pulse. After being through with all the channels, this counter is reset. This reset pulse clocks the 10 bit counter and is incremented by one, thereby pointing to next location in the memory of the first 1K block.

The write address generator circuit is shown in the overall circuit diagram. Refer to fig(3.9)

FIG 3.7

• •

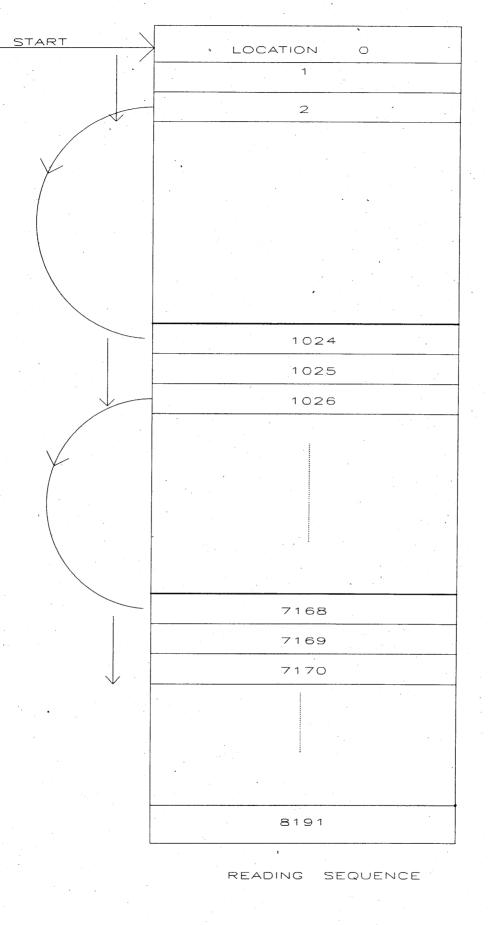

## B. E. (E & C) Final Year Project 1994–95 Bangalore University (b) Read Address Generator:

The data stored in the memory has to read out sequentially into the FFT card. All data points stored in one 1k block, which corresponds to the data from one channel, are read first before going over to the next 1k block and the process is repeated.

This means that the address pointer has to be incremented by one at every clock pulse and after reading N<sub>p</sub> points, has to be incremented to the starting position of next 1k block. The sequence of read address generated is shown in fig(3.8).

In order to achieve this sequence of addressing the address generator is built by cascading 10 bit and 3 bit counters. But in this case the 10 bit counter is clocked by the master clock. This will cause the address pointer to be incremented by one at every clock. When the output of this counter is clocks the 3 bit counter.

Hence, the address generator will now point to the starting location of the next 1kB block. The read address generator circuit is shown in the overall circuit diagram. *Refer to fig(3.9)*

#### Address Multiplexer:

With both S-RAMs involved in read and write operations, the two of them will have to be provided with both the read and write address sequences. So the outputs of the two address generators are time multiplexed, and the outputs of the multiplexer forms the address bus of the two memories. The control bits for the multiplexer are provided by the status registers. The address multiplexer is as indicated in the overall circuit diagram. *Refer to fig* (3.9).

FIG 3.8

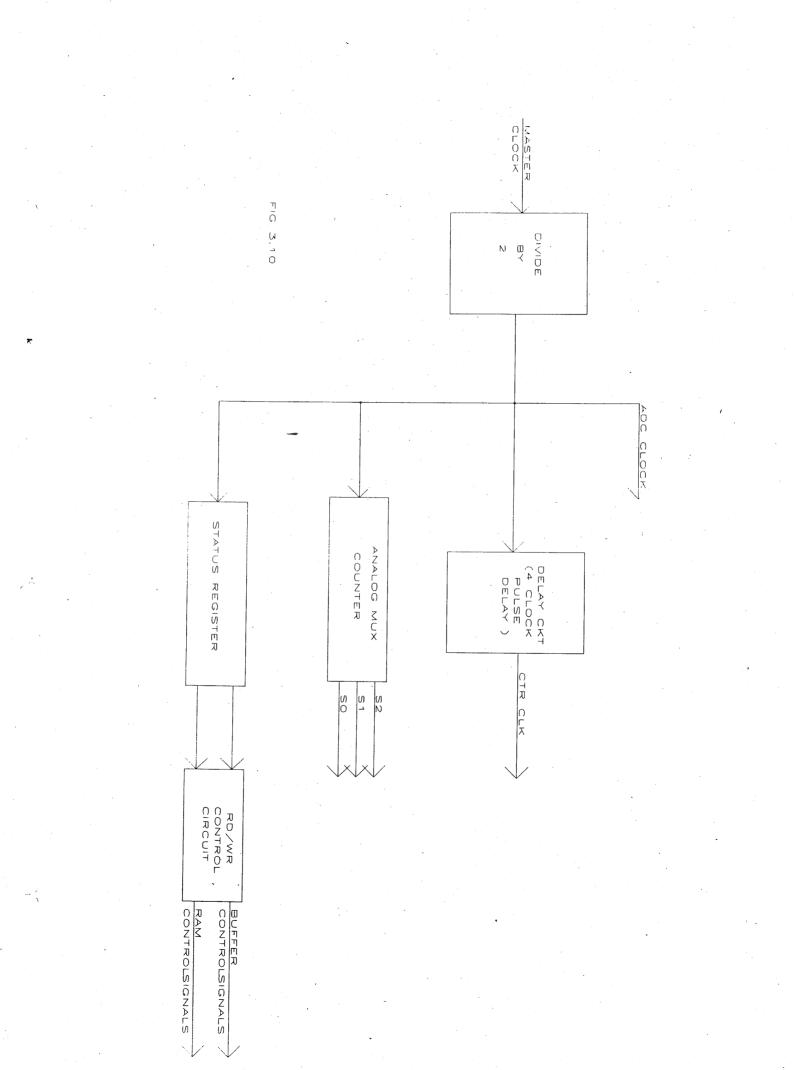

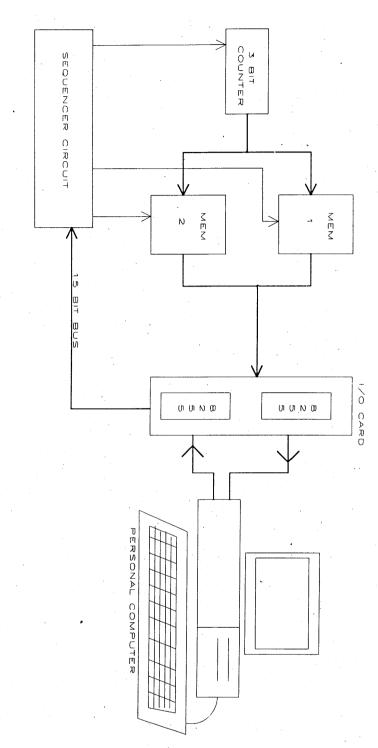

# B. E. (E & C) Final Year Project 1994–95 Bangalore University 3.3 <u>CLOCK CONTROL CIRCUIT:</u>

The clock control circuit is used for providing appropriate clock pulses to the various functional blocks. It is fed with a master clock from an external circuit. The clock signals provided are :

- Memory address clock: clock for the memory address generators.

- Read and Write control signals: enabling signals for the S- RAMs and buffers.

- Clock Control for Analog circuitry: clocking pulses for the ADC, sampling clock for sample and hold circuits.

The method of generation of various signals is represented schematically in fig(3.10).

#### **Clock for Memory Address Generators:**

The ADC being a pipe lined device has a delay of 4 clock pulses, between an analog signal being given at its input and the corresponding digitized data appearing at the ADC output. The digital data from the ADC is then written into SRAMs. So the address generators used for generating writing address should start only after this delay. A 3 bit synchronous self stopping counter is used for this purpose. The output of this counter is decoded and used to enable clock to the address generator.

## B. E. (E & C) Final Year Project 1994–95

#### Bangalore University

At the time of power up or any ensuing initialization of the *BDR* this 3 bit counter is also cleared. It then accumulates 4 counts. On the 5<sup>th</sup> pulse this counter is stopped and the clock to the read and write address generator is enabled. The appropriate waveforms are indicated in fig(3.11).

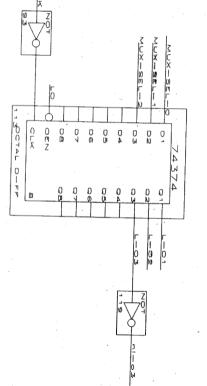

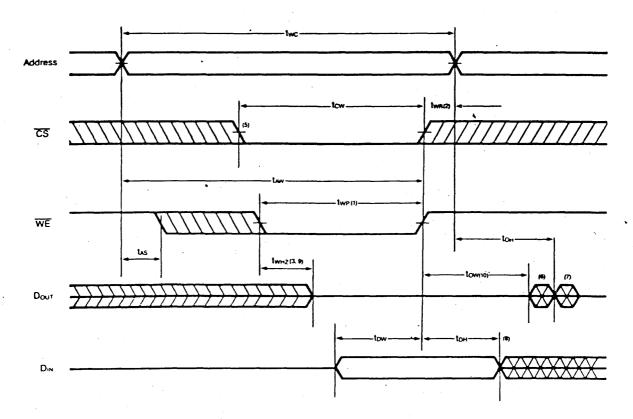

#### **Read/Write Control Signals:**

The two SRAMs and their associated buffers need control pulses, like output enable, write enable etc., for their operation. The read write controller in the clock control circuit generates these control pulses. The operation of each control pulse is discussed below briefly.

- <u>BUF-OE</u>: It is used to control the output of the buffer When BUF-OE is low, output of the buffer is enabled and with BUF-OE high, the output is tri-stated.

- **RAM-OE**: This signal enables the output of the SRAMs. With RAM-OE low the data can be read out of the memory and if it is high the memory may be used for writing (if WR = 1). If RAM-OE is high output of memory will be tri-stated.

- <u>**RD/WR**</u>: This signal controls the state of the SRAMs, that is, it decides whether data can be written into the SRAM or read from it.

The read write controller logic circuit is indicated in the overall circuit diagram. The two D type flip-flops are so connected that their outputs are perpetually complements of each Dept. of E & C Engineering, **R.V.C.E.** Bangalore

### B.E. (E&C) Final Year Project 1994-95

#### Bangalore University

other. Their outputs have been used to dictate the generation of the control pulses and thereby decide the status of the two memories (which is why the two of them together have termed as status registers). In fact, they give a clear indication of which memory is in read cycle and which is in the write cycle.

The RD/WR and RAM-OE signals should be pulses of duration less than the clock given to the counter to, prevent data being duplicated or overwritten in the memories. Different conditions resulting from different values of  $WE_1$  and  $WE_2$  are discussed below briefly:

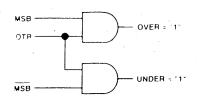

- $WE_1 = 0$  and  $WE_2 = 1$ : With  $WE_1 = 0$  AND<sub>1</sub> is disabled and AND<sub>2</sub> is enabled. The output of the XOR<sub>2</sub> will be same as the pulse given to AND<sub>1</sub> (since WE<sub>1</sub>=0). The output of the XOR<sub>1</sub> will be continuously high (WE<sub>2</sub> = 1).

- $WE_1 = 1$  and  $WE_2 = 0$ : With  $WE_1 = 1$  AND<sub>1</sub> is enabled and AND<sub>2</sub> is disabled. The output of XOR<sub>1</sub> will be pulsating and output of XOR<sub>2</sub> will be in high state continuously.

The RD/WR<sub>1</sub> and RD/WR<sub>2</sub> signal are also used to control the output of SRAM<sub>1</sub> and SRAM<sub>2</sub>.

k

The logic discussed above has been programmed into EPM 7128LC84. The details of which are provided in the *Appendix D*. The final schematic of the *BDR* is also included in the following page.

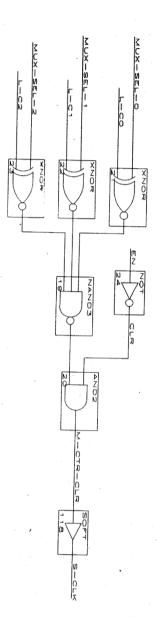

### **Analog clock Generators:**

There are three signals that the digital control circuits have to provide the analog part of the circuit with, namely:

- ADC clocking

- Analog MUX selection

- Sampling clock for sample and hold circuits

The ADC clock frequency is same as the memory address clock frequency. It is directly provided by the clock controller.

The Analog MUX selection bits are generated by a 3 bit synchronous counter, which is clocked by ADC clock. Since this MUX has to switch between the selected number of channels, the counter has been made programmable. As earlier the PC, during the time of initializing the *BDR* card programs this counter also. The sampling clock is the signal given to the sample and hold circuits for putting them into the hold state. It is generated at the of  $(1/N_c)$  times the ADC clocking frequency, where N<sub>c</sub> is the number of channels input.

The circuit diagram of the analog clock control circuit is shown in fig(3.12).

ADC-C

AVALOG MUX SELECTION

.

ūίο Ο

6

## **MEMORY BANK:**

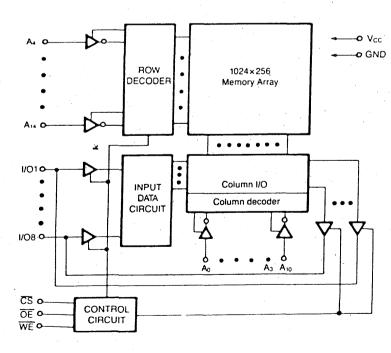

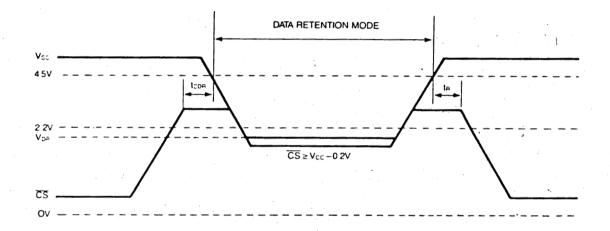

The memory bank consists of two HY62C256/L ICs which are 32,768 word by 8-bit CMOS Static RAMs, of which only 8k have been put to use. The HY62C256/L has a typical access time of 100ns. The need for two such devices has been explicitly explained in previous chapters. Further details about HY62C256/L can be found in *Appendix D*.

## CHAPTER FOUR TESTING AND CONCLUSION

## 4.1 TESTING OF DIGITAL CONTROL LOGIC

First the logic of the control system implemented using EPLD are tested. This is done by entering the required logic in to the graphic editor file of MAX + PLUS-2 (details of MAX +PLUS II are in *Appendix C* and then simulating its functioning. Two levels of simulation are done:

**Software Simulation:** It is done before programming the logic into the EPLD. The desired inputs to the EPLD are entered into a simulator file as waveforms. The logic simulator on MAX + PLUS-2 is then used to run a simulation of this file. The simulated outputs are observed in the simulator file. It is found to be in agreement with the desired results.

Hardware Simulation: The logic discussed earlier in *chapter 3* is fused into a EPLD (EPM 7128) by the programmer of MAX + PLUS-2. For this the EPLD is placed in the MAX + PLUS-2 programming module. The programmed EPLD is now used to perform hardware simulation, i.e., the input signals (entered in simulator file) are generated from the PC and sent to the EPLD (placed in the adapter module). The EPLD outputs are monitored and this outputs are found to match with software output.

The buffered data router being developed is a prototype board. It is therefore first implemented on general purpose PCB. This would help us make modifications, if necessary, in case of bugs found in the circuit, which would be a trouble-some process with a custom made PCB.

Due to the non-availability of the required analog components at the right time, the Analog conditioning and digitizer circuit could not be implemented. So it was decided that the **BDR** and its associated control logic must be tested independent of these analog components.

This can be achieved by a digital circuit that would simulate the output of the ADC. The output of such a digital circuit should preferably sequential and synchronous with the **memory** address clock. This will allow us to predict the output of the data router card effectively.

The digital circuit involved is a simple 3 bit counter. This 3 bit counter, called the test counter, is clocked at the same rate as the address generators (with necessary compensation for ADC pipe line delay).

Since the DSC itself is PC based, it is only apt that this project, the buffered data router is also PC based. The PC is used to initialize the Buffered Data Router (**BDR**), during which the number of channels and number of points the user specifies are loaded into the card. The interface between the PC and the **BDR** CARD is a 48 line I/O port (a 8255 based card, containing two 8255A chips). The card details can be obtained in *Appendix D*.

#### **B. E.** (E & C) Final Year Project 1994–95

#### Bangalore University

The 48 lines of the 8255 card have been split into two groups (1) 24 lines for input (2) 24 line for output. Out the 24 output lines 16 have been used: 11 for loading number of points, 4 for loading number of channels, one line for sending the enable pulse at the time of initialization.

Initializing the **BDR** and configuring the ports of I/O card is accomplished by a program written in C language. The program source code is given in the following page.

The program itself is user friendly and interactive. The tasks of initialization, acquisition and browsing of acquired data have been made very simple with self explanatory menus.

Incidentally, a second 8 bit bus from the **BDR** sends the output data from the data router to the PC via the input port of the 8255 I/O card.

With write address being incremented by 1024 at every clock pulse (while the test counter is incremented by 1), a different number is written into each 1 kB block of the 8 kB memory. The numbers stored adjacent memory block will therefore differ by one. The data stored in memories are read out sequentially. Thereby reading all the number stored in a 1k block before going over to the next (1k block). The output sequence can now predicted. Each number is number will be repeated N<sub>p</sub> number of times. The block diagram of the test circuitry is shown in fig(4.1).

The PC clock and clock given **BDR** being different will not be synchronous. So the data output from **BDR**, may not be synchronized with the inport instruction executed by the

```

# include <stdio.h>

# include <conio.h>

# include <dos.h>

# include <time.h>

# define TRUE

1

# define FALSE

O

static int arr[8192],flag=1,lflag=FALSE,pjunk=0,col,temp;

unsigned int points=1025, temp_points, chanls=9;

unsigned int byte_1=0x00ff,byte_2=0x000f;

void main()

{

clrscr();

accept_pts_chnls();

load card();

acquire_data();

save_file();

}

--- accept_pts_chnls() ----

1*----

---*/

accept_pts_chnls(void)

{

lflag = FALSE;

points=1025;

chanls=9;

byte 1=0x00ff;

byte_2=0x000f;

while (points < 0 || points > 1024)

gotoxy(21,11);

printf("Enter the no. of points [Max-1024] : ");

scanf("%4d",&points);

3

temp_points=points;

while (chanls < 0 \| chanls > 8)

£

gotoxy(25,11);

printf("Enter no. of chanls [Max-8] : ");

scanf("%id",&chanls);

}

```

```

byte_1=byte_1 & points;

byte_2=byte_2 & chanls;

byte_2=byte_2 << 3;</pre>

points=points >> 8;

byte_2=byte_2 '| points;

gotoxy(22,4);

lflag = TRUE;

return:

}

---- END OF FUNCTION ACCEPT PTS CHNLS ------*/

load_card(void)

{

i*

port addresses

PORT A -- 0x600

PORT B -- 0x601

PORT C -= 0x602

CONTROL PORT 0x603

*/

outportb(0x603,0x80); /* configure all the

ports of 8255 as outputs */

delay(1);

outportb(0x602,0x00); /* initially make EN low */

delay(1);

outportb(0x600,byte_1); /* output npint and nchnl

to the card. */

delay(1);

/* PA7 PA6 PA5 PA4 PA3 PA2 PA1

PA0 */

outportb(0x601,byte_2); /* 7

5

6

4

3

2

NPINTO */

1

delay(1);

/*

PB7 PB6 PB5 PB4

PB3

PB2 PB1 PB0 */

/*

3

2

CHNLO

1

10 9 NPINT8 */

outportb(0x602,0xff);

/* now make EN high */

delay(1);

return;

/*

----- END OF FUNCTION LOADCARD -

----*/

```

```

/*----- ACQUIRE DATA() ------

acquire_data(void)

int s;

outportb(0x607,0x9b);

gotoxy(9,18);

textcolor(YELLOW);

gotoxy(10,20);

outportb(0x602,0x00); /* make EN low */

delay(1);

for(s=0:s<8192:s++)

£

while(inportb(0x606)==0);

arr[s]=inportb(0x604);

if(s \times 130 = = 0)

cprintf("%c",219);

while(inportb(0x606)!=0);

}

return;

}

----- END OF FUNCTION ACQUIREDATA -----*/

/*

/* ------ UDF : Saves data acuired from memory -----*/

save_file(void)

{

auto int h;

FILE *fptr;

fptr = fopen("sample.dat", "w");

cprintf(" Downloading data from SYSTEM RAM

"):

gotoxy(19,14);

cprintf("

to a new file SAMPLE.DAT .

"):

gotoxy(19,15);

cprintf("

");

Please wait .....

for(h=0;h<=8191;h++)</pre>

fprintf(fptr,"%d ",arr[h]);

if((h+1)%temp_points==0) fputc('\n',fptr);

fclose(fptr);

return;

}

/*

---- END -----

---*/

```

<u>ๆ</u> ถ

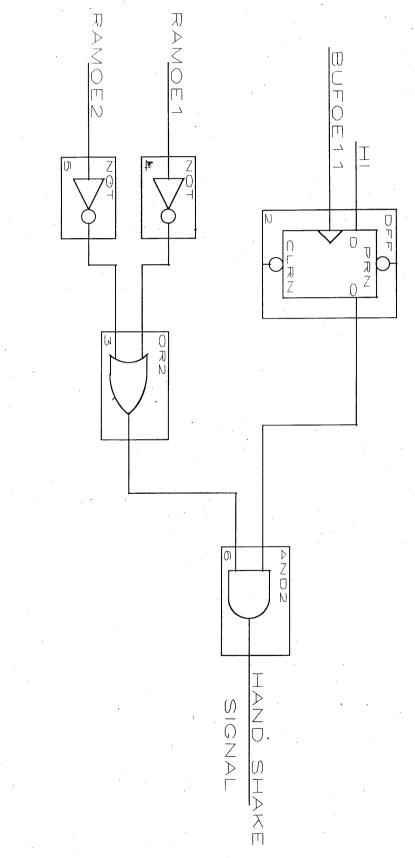

4 . 1

PC. This leads to the same data being read twice or it being completely lost. To overcome this problem, the synchronization circuit is used period. The output enable signal of the two SRAMs has been used to generate a **Data Ready Signal (DRS)** as shown in fig(4.2). This would inform the PC when fresh data has been put on the data bus. Care has also been to taken to prevent acquisition of data during the very first write cycle when the content of the one of the memory chips is invalid. The program will polling for this data ready signal and acquires a data point, at every DRS. This forms the necessary hand shake signal between the **BDR** and the host CPU or the DSC.

This data is stored in the memory of the PC, which can be down loaded into a file, in ASCII format, if the user so wishes. This allows for storing away the acquired data in the hard disk for later use. Since the data is stored in ASCII format any text editor can be used to view the contents of the file.

The *Buffered Data Router* was tested extensively in the afore said method. The card performed according to the specifications.

CIRCUIT DIAGRAM OF SYNCHRONISATION CIRCUIT

Г С 4.2

## **CONCLUSION**

The Multi channel digitizer card combined with the Buffered Data Router is a versatile tool in the field of data acquisition systems. It has ability to be programmed through a IBM 80x86 PC, with the help of menu driven program.

The most important feature of the Buffered Data Router, is that it can effectively convert a single DSC into a multi-channel one, without affecting the speed of the DSC. It can assist in General Spectral Analysis apart from using it for studying CRRLs.

The Analog Multiplexer forms a bottleneck in the entire system, with its high settling time. This again can be remedied easily, because this circuit has also been implemented on a separate PCB.

A very high speed ADC has been included into the circuit, on a separate PCB. The speed of the ADC is sufficing for all practical purposes. But in the future, if the need be, the ADC can be replace with a faster one, on availability of such a device. It can also be function as a laboratory spectrum analyzer.

Other than that the system can perform as a multi-channel data acquisition system. A data ready signal incorporated into the system can be used for synchronizing the board with the next stage.

## APPENDIX A

### **GEETEE**

The Gauribidanur Radio Telescope is of the ARRAY type operating at 34.5 MHz center frequency with a bandwidth of 2 MHz. It is essentially a **meridian transit instrument**. The telescope consists of 1,000 broad band dipoles arranged in the form of the letter "**T**". The outputs of four dipoles along East West (EW) direction are combined in a Christmas tree fashion using open wire (balanced) transmission lines, and transformers to form a "basic array element."

Such basic array elements, numbering two hundred and fifty are arranged to form a 1.38 km long EW array along the East West direction. Similarly ninety basic array elements are arranged to form a 0.45 km long south array along the south direction from the center of the EW array. The signals from the basic array units are brought to the laboratory through open wire transmission lines. East West array has an effective collecting area of approximately 12,000 m<sup>2</sup>, while that of the North South array is approximately 7,000 m<sup>2</sup>.

The receiver permits observation of a 15° patch of sky (in the N-S direction) with 46 beams. The resolution is 26 X 40 sec ZA (ZA is the zenith angle). The sensitivity is around 20 Jansky.

## APPENDIX B

2

## B. E. (E & C) Final Year Project 1994-95 Bangalore University CARBON RADIO RECOMBINATION LINES [CRRLs]

These lines involve highly excited states, presumably of carbon, during the transient recombination of a carbon ion with an electron. These lines(representing the highest excited states yet detected in interstellar gas) should be valuable indicators of conditions in the interstellar medium. Assuming carbon as the element involved, the presumed scenario is that a singly ionized carbon ion (C<sup>+</sup>) recombines briefly with an electron. The resulting neutral, but highly excited states accompanied by emission or absorption. The higher the excitation, the more numerous and closely spaced the lines become so that the energies of transition ( $\eta \varpi$ ) and the resulting frequencies( $\nu$ )are less with many falling below 100 MHz.

The twelve CRRLs are listed below;

| Sl. no. | Orbital Quantum Number 'n' | Frequency in MHz |

|---------|----------------------------|------------------|

| 1       | 570                        | 35.43389892      |

| 2       | 571                        | 35.24821929      |

| 3       | 572                        | 35.06383472      |

| 4       | 573                        | 34.88073395      |

| 5       | 574                        | 34.69890580      |

| 6       | 575                        | 34.51458867      |

| 7       | 576                        | 34.33476567      |

| 8       | 577                        | 34.16094739      |

| 9       | 578                        | 33.98410055      |

| 10      | 579                        | 33.63405521      |

| 11      | 580                        | 33 63405215      |

| 12      | 581                        | 34.47971491      |

The above frequencies were calculated using the below formula;

$F = 3.2896919 \times 10^9 [1/n^2 - 1/(n+1)^2]$  MHz

where 'n' is the orbital quantum number.

## APPENDIX C

ñ.

## MAX + PLUS AND EPLD

MAX+PLUS - the MAX programmable logic user system from Altera Corporation is a "fully integrated package for developing and implementing custom logic circuits with Altera's Multiple Array Matrix (MAX) family of high density Erasable Programmable Logic Devices (EPLDs)". The MAX+PLUS software offers different ways to enter the circuit design, compiles and fits the design to use MAX architecture in the most efficient way possible, and generates a file for programming the EPLD. One can also simulate the logic and timing characteristics of the design. The MAX + PLUS hardware consists of a software controlled Logic Programming Unit used for device programming.

Programmable logic devices (known by various names such as PAL, PLA, PLD, EPLD etc.) combine the logistical advantages of standard, fixed integrated circuits with the architectural flexibility of custom devices. They allow to electrically program standard, off the shelf logic elements to meet the specific needs of their applications. This eliminates various problems due to use of individual ICs in a circuit and reduces the overall cost and the time for the design.

The fundamental building block of an EPLD is the "macrocell". Each macrocell consists of three parts.

(1) The logic array that implements all combinatorial logic functions.

(2) The programmable register that provides D, T, JK or SR flip-flops.

(3) Programmable I/O that allows each I/O pin to be configured as input, output, or bi-directional operation.

#### **B. E.** (E & C) Final Year Project 1994–95

Bangalore University

The logic array consists of a programmable AND/fixed-OR PLA array. Inputs to the AND array come from the true and complement of the dedicated input and clock pins, and from the macrocell and I/O feedback paths. The connections between them are opened during the programming process.

Programmable flip-flop are used to create a variety of logic functions that use a minimum of EPLD resources. If the flip flop is not required for macrocell logic, it may simply be bypassed. In general purpose EPLDs each flip flop may be clocked from a dedicated system clock, any input or I/O pin or any internal logic function. EPLD registers are positive edge triggered with data transitions that occur on the positive edge of the clock. In addition, gated clock and clock enable logic can be implemented but their delay time is larger.

The EPLD I/O control block contains a tri-state buffer controlled by a ,macrocell product term and drives the I/O pin. I/O pins may be configured as dedicated outputs, bidirectional outputs, or as additional dedicated inputs.

The EPLDs have been, built using the "CMOS EPROM " technology. The density of the chips range from hundreds to thousands of gates, offered in variety of packages with 20 to 100 pins.

EPLD families are divided into two architectural categories. The first one is the general purpose group which provide maximum flexibility for general purpose logic replacement. The EP series and EPM5000 series come under this group. The second group are the function

Dept. of E & C Engineering, **R.V.C.E.** Bangalore

## **B. E.** (E & C) Final Year Project 1994–95 Bangalore University

specific EPLDs specialized for performing specific system design tasks. The EPB and EPS series constitutes this group.

EPLDs are offered in a variety of packages including the dual in-line package (DIP), J-lead chip carrier (JLCC), Quad Flat Pack (QFP), Pin Grip Array (PGA) etc. EPLDs which are re-programmable are provided with windows are made of ceramic whereas, for high volume production one-time programmable plastic versions are available.

As already explained, the MAX+PLUS software is used for programming the chips.

<u>APPENDIX D</u>

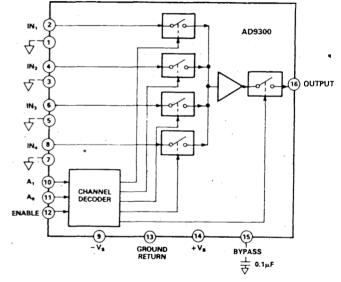

## 4 × 1 wideband Video Multiplexer

#### FEATURES

34MHz Full Power Bandwidth ±0.1dB Gain Flatness to 8MHz 75dB Crosstalk Rejection @ 10MHz 0.05°/0.05% Differential Phase/Gain Cascadable for Switch Matrices

#### APPLICATIONS

Video Routing Medical Imaging Electro-Optics ECM Systems Radar Systems Data Acquisition

#### GENERAL DESCRIPTION

The AD9300 is a monolithic high-speed video signal multiplexer useable in a wide variety of applications.

Its four channels of video input signals can be randomly switched at megahertz rates to the single output. In addition, multiple devices can be configured in either parallel or cascade arrangements to form switch matrices. This flexibility in using the AD9300 is possible because the output of the device is in a high-impedance state when the chip is not enabled; when the chip is enabled, the unit acts as a buffer with a high input impedance and low output impedance.

An advanced bipolar process provides fast, wideband switching capabilities while maintaining crossstalk rejection of 75dB at 10MHz. Full power bandwidth is a minimum 30MHz. The device can be operated from  $\pm 10V$  to  $\pm 15V$  power supplies.

The AD9300KQ is packaged in a 16-pin ceramic DIP and is designed to operate over the commercial temperature range of 0°C to +70°C. For military temperatures of -55°C to +125°C, order part number AD9300TQ, which is also a 16-pin ceramic DIP. In addition to DIP packages, the AD9300 is also available in a' 20-pin LCC as the model AD9300TE, which operates over a temperature range of -55°C to +125°C.

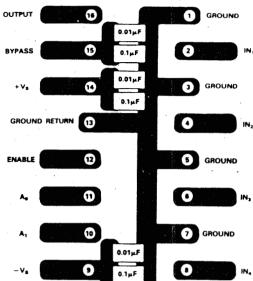

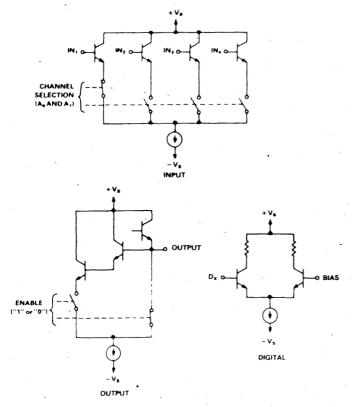

AD9300 Functional Block Diagram (Based on Cerdip)

#### **ORDERING INFORMATION**

| Device   | Temperature<br>Range | Description                         |  |

|----------|----------------------|-------------------------------------|--|

| AD9300KQ | 0 to + 70°C          | 16-Pin Cerdip, Commercial           |  |

| AD9300TQ | - 55°C to + 125°C    | 16-Pin Cerdip, Military Temperature |  |

| AD9300TE | - 55°C to + 125°C    | 20-Pin I.CC, Military Temperature   |  |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

)

One Technology Way; P. O. Box 9106; Norwood, MA 02062-9106 U.S.A.

Tel: 617/329-4700

Twx: 710/394-6577

Telex: 924491

Cables: ANALOG NORWOODMASS

## SPECIFICATIONS

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltages $(\pm V_S)$                    |

|------------------------------------------------|

| Analog Input Voltage Each Input ± 3.5V         |

| $(IN_1 thru IN_4)$                             |

| Differential Voltage Between Any Two           |

| Inputs (IN <sub>1</sub> thru IN <sub>4</sub> ) |

Digital Input Voltages ( $A_0$ ,  $A_1$ , ENABLE) -0.5V to +5.5V

| Output Current              | •                                         |

|-----------------------------|-------------------------------------------|

| Sinking                     | 6.0mA                                     |

| Sourcing                    | 6.0mA                                     |

| Operating Temperature Range |                                           |

| AD9300KQ                    | $ 0^{\circ}C \text{ to } + 70^{\circ}C$   |

| AD9300TQ/TE                 | $ 55^{\circ}C to + 125^{\circ}C$          |

| Storage Temperature Range   | $ 65^{\circ}C \text{ to } + 150^{\circ}C$ |

| Junction Temperature        | · · · · · · · · · + 175°C                 |

| Lead Soldering (10sec)      | +300°C                                    |

## **ELECTRICAL CHARACTERISTICS** ( $\pm V_s = \pm 12V \pm 5\%$ ; C<sub>L</sub> = 10pF; R<sub>L</sub> = 2k $\Omega$ , unless otherwise noted)

|                                                          |          | Test              |       | DMMEF<br>) to +70 | CIAL<br>C   | 10pr; ng - 2k                     | - 55      | AILITA<br>°C to +1 | RY<br>25°C      |         |

|----------------------------------------------------------|----------|-------------------|-------|-------------------|-------------|-----------------------------------|-----------|--------------------|-----------------|---------|

| Parameter (Conditions)                                   | Temp     | Level             | Min   | AD9300H<br>  Typ  | (Q<br>  Max | Military<br>Subgroup <sup>2</sup> | AD<br>Min | 9300TQ             | / I E<br> - Max | Units   |

| INPUT CHARACTERISTICS                                    | +        | +                 |       |                   | <u>+</u>    |                                   | +         | <u> </u>           | <b>+</b>        | +       |

| Input Offset Voltage                                     | + 25°C   | I                 |       | 3                 | 10          | 1                                 | 1         | 3                  | 10              | mV      |

| Input Offset Voltage                                     | Full     | VI                |       | د                 | 10          | 2,3                               |           | J                  | 18              | mV      |

|                                                          | Full     | V                 |       | 75                | 14          | 2,5                               |           | 83                 | 10              | , μV/°C |

| Input Offset Voltage Drift <sup>3</sup>                  | -        |                   | •     | 1                 | 377         |                                   | 1         |                    |                 |         |

| Input Bias Current                                       | + 25°C   | I                 |       | 15                | 37          | 1.                                |           | 15                 | 37              | μA      |

| Input Bias Current                                       | Full     | VI                | 1     |                   | 55          | 2,3                               | 1         |                    | 55              | μA      |

| Input Resistance                                         | + 25°C   | V                 |       | 3.0               |             |                                   |           | 3.0                | 1               | MΩ      |

| Input Capacitance                                        | + 25°C   | V                 |       | 2                 |             |                                   |           | -2                 | 1               | pF      |

| Input Noise Voltage (dc to 8MHz)                         | + 25℃    | v                 |       | 16                | 1           |                                   |           | 16                 |                 | μVrms   |

| <b>FRANSFER CHARACTERISTICS</b>                          | 1        |                   |       |                   |             | [                                 |           |                    |                 | 1       |

| Voltage Gain <sup>4</sup>                                | + 25°C   | Ι                 | 0.990 | 0.994             |             | 1                                 | 0.990     | 0.994              |                 | V/V     |

| Voltage Gain <sup>4</sup>                                | Full     | VI                | 0.985 |                   |             | 2,3                               | 0.985     |                    |                 |         |

| DC Linearity <sup>5</sup>                                | + 25°C   | v                 |       | 0.01              |             |                                   |           | 0.01               | 1               | 0%      |

| Gain Tolerance ( $V_{IN} = \pm 1V$ )                     |          |                   |       |                   |             |                                   |           | i                  |                 | 1       |

| dc to 5MHz                                               | + 25°C   | I                 |       | 0.05              | 0.1         | 4                                 |           | 0.05               | 0.1             | dB      |

| 5MHz to 8MHz                                             | + 25°C   | I                 |       | 0.1               | 0.3         | 4                                 |           | 0.1                | 0.3             | dB      |

| Small-Signal Bandwidth                                   | + 25°C   | v                 |       | 350               |             |                                   |           | 350                |                 | MHz     |

| (V <sub>IN</sub> 100mV p-p)                              | 1 - E    | 1                 | 1     |                   |             |                                   | -<br>-    | • .<br>•           | !               | :       |

| Full Power Bandwidth <sup>6</sup>                        | + 25°C   | I                 |       | 34                | i           | 4                                 | 30        | 34                 | 1               | MHz     |

| $(V_{IN} = 2V p - p)$                                    |          | -                 |       |                   |             |                                   | 1         | -                  | 1               |         |

| Output Swing                                             | Full     | VI                | ±2    |                   |             | 1,2,3                             | ± 2       |                    | •               | v       |

| Output Swing Output Current (Sinking $(a = 25^{\circ}C)$ | + 25°C   | v                 |       | 5                 |             | ., ., .                           |           | 5                  | 1               | mA      |

| Output Resistance                                        | + 25°C   | III               |       | 9                 | 15          | 12                                | 1         |                    | 15              | Ω       |

| · · · · · · · · · · · · · · · · · · ·                    |          |                   |       |                   | 1.5         |                                   | ļ         |                    |                 | · ••    |

| DYNAMIC CHARACTERISTICS                                  |          | 1 -               |       |                   |             |                                   |           |                    |                 |         |

| Slew Rate                                                | + 25°C   | I                 | 190   | 215               |             | 4                                 | 190       | 215                | 1               | V/µs    |

| Settling Time                                            |          |                   |       |                   |             | · .                               |           |                    |                 |         |

| $(to 0.1\% on \pm 2V Output)$                            | + 25°C   | III               |       | 70                | 100         | 12                                |           | 70                 | 100             | ns      |

| Overshoot                                                | 1        |                   |       |                   |             |                                   |           |                    |                 |         |

| To T-Step <sup>8</sup>                                   | + 25°C   | V                 |       | -:0.1             |             |                                   |           | < 0.1              |                 | %       |

| To'Pulse <sup>9</sup>                                    | + 25℃    | v                 |       | 10                |             |                                   |           | <10                |                 | %       |

| Differential Phase <sup>10</sup>                         | + 25°C   | III               |       | 0.05              | 0.1         | 12                                |           | 0.05               | 0.1             | 1 2 · · |

| Differential Gain <sup>10</sup>                          | + 25°C   | ш                 |       | 0.05              | 0.1         | 12                                |           | 0.05               | 0.1             | 0,0     |

| Crosstalk Rejection                                      |          |                   |       |                   |             |                                   |           |                    |                 |         |

| Three Channels <sup>11</sup>                             | + 25°C   | I                 | 70    | 75 i              |             | 4                                 | 70        | 75                 |                 | dB      |

| One Channel <sup>12</sup>                                | + 25°C   | I                 | 80    | 83                |             | 4                                 | 80        | 83                 |                 | dB      |

| WITCHING CHARACTERISTICS <sup>13</sup>                   | <u>+</u> |                   |       |                   |             |                                   |           |                    |                 |         |

| A <sub>X</sub> Input to Channel HIGH Time <sup>14</sup>  | + 25°C   | I                 |       | 40                | 50          | 9                                 |           | 40                 | 50              | ns      |

|                                                          | 1230     | •                 |       | 70                |             | ,                                 |           | 70                 | 50              | 115     |

| (t <sub>HIGH</sub> )                                     | 1,200    | I                 |       | 25                | 45          | 9.                                |           | 35                 | 45              | DC      |

| A <sub>X</sub> Input to Channel LOW Time <sup>15</sup>   | + 25°C   | ľ                 |       | 35                | 43          | 7                                 | ÷         | 22                 | 43              | ns      |

| $(t_{LOW})$                                              | 1 2500   | ,                 |       | 20                | - 10        | 9 1                               |           | 20                 | 10              |         |

| Enable to Channel ON Time <sup>16</sup>                  | + 25°C   | I                 |       | 30                | 40          | · Y                               |           | 30                 | 40              | ns      |

| $(t_{ON})$                                               | 2000     |                   | ł     |                   |             |                                   | 1         |                    |                 |         |

| Enable to Channel OFF Time <sup>1*</sup>                 | + 25°C   | 1                 |       | 20                | 30          | 9                                 |           | 20                 | 30              | ns      |

| (L <sub>OFF</sub> )                                      |          |                   | i     |                   |             |                                   |           |                    | ĺ               |         |

| Switching Transient <sup>18</sup>                        | + 25°C   | $\mathbf{V}_{ij}$ | 1     | 60                |             |                                   |           | 60                 |                 | mV      |

-2-

|                                                               | -     |               |                                        | OMME<br>0 to + 70<br>AD9300 | °C                |                                   | - 55  | AILITA<br>°C to + 1<br>9300TQ | 25°C |       |

|---------------------------------------------------------------|-------|---------------|----------------------------------------|-----------------------------|-------------------|-----------------------------------|-------|-------------------------------|------|-------|

| Parameter (Conditions)                                        | Temp  | Test<br>Level | Min                                    | Тур                         | Max               | Military<br>Subgroup <sup>2</sup> | Min   | Тур                           | Max  | Units |

| DIGITAL INPUTS                                                | •     | 3<br>7<br>1   | •••••••••••••••••••••••••••••••••••••• | •··- ····                   |                   |                                   | • ••• | •                             |      | 1     |

| Logic "1" Voltage                                             | Full  | VI            | 2                                      | 1                           | 1                 | 1,2,3                             | 2     |                               |      | v     |

| Logic "0" Voltage                                             | Full  | VI            | ÷ .                                    |                             | 0.8               | 1,2,3                             |       |                               | 0.8  | v     |

| Logic "1" Current                                             | Full  | VI            | :                                      |                             | 5                 | 1,2,3                             |       |                               | 5    | μA    |

| Logic "0" Current                                             | Full  | VI            | -                                      |                             | 1                 | 1,2,3                             |       |                               | 1    | μA    |

| POWER SUPPLY                                                  | •     |               | ∔                                      |                             | • · · · · · · · · | •                                 | • • • | • • • • •                     |      |       |

| Positive Supply Current (+ 12V)                               | + 25℃ | 1             |                                        | 13                          | 16                | 1                                 |       | 13                            | 16   | mA    |

| Positive Supply Current (+12V)                                | Full  | VI            |                                        | 13                          | 16                | 2,3                               |       | 13                            | 16   | mA    |

| Negative Supply Current (-12V)                                | +25℃  | I             | 1                                      | 12.5                        | 15                | 1                                 |       | 12.5                          | 15   | mA    |

| Negative Supply Current (-12V)                                | Full  | ·VI           |                                        | 12.5                        | 16                | 2,3                               |       | 12.5                          | 16   | mA    |

| Power Supply Rejection Ratio<br>$(\pm V_s = \pm 12V \pm 5\%)$ | Full  | VI            | 67                                     | 75                          |                   | 1,2,3                             | 67    | 75                            | · .  | dB    |

| Power Dissipation $(\pm 12V)^{19}$                            | +25℃  | v             |                                        | 306                         |                   |                                   |       | 306                           |      | mW    |

NOTES

)

<sup>1</sup>Permanent damage may occur if any one absolute maximum rating is exceeded. Functional operation is not implied, and device reliability may be impaired by exposure to higher-than-recommended voltages for extended periods of time.

<sup>2</sup>Military Subgroups apply to military-qualified devices only.

<sup>3</sup>Measured at extremes of temperature range.

<sup>4</sup>Measured as slope of  $V_{OUT}$  versus  $V_{IN}$  with  $V_{IN}$

- + IV. <sup>5</sup>Measured as worst deviation from end-point fit with  $V_{IN} = \pm 1V$ .

<sup>6</sup>Full Power Bandwith (FPBW) based on Slew Rate (SR). FPBW = SR/2 $\pi$ V<sub>PEAK</sub>

<sup>7</sup>Measured between 20% and 80% transition points of ±1V output.

<sup>8</sup>T-Step = Sin<sup>2</sup>X Step, when Step between 0V and +700mV points has 10%-to-90% risetime = 125ns.

<sup>9</sup>Measured with a pulse input having slew rate  $>250V/\mu s$ .

$^{10}$ Measured at output between 0.28Vdc and 1.0Vdc with V<sub>IN</sub> = 284mV p-p at 3.58MHz and 4.43MHz.

<sup>11</sup>This specification is critically dependent on circuit layout. Value shown is measured with selected channel grounded and 10MHz 2V p-p signal applied to remaining three channels. If selected channel is grounded through 75 $\Omega$ , value is approximately 6dB higher.

<sup>12</sup>This specification is critically dependent on circuit layout. Value shown is measured with selected channel grounded and 10MHz 2V p-p signal applied to one other channel. If selected channel is grounded through 75Ω, value is approximately 6dB higher.

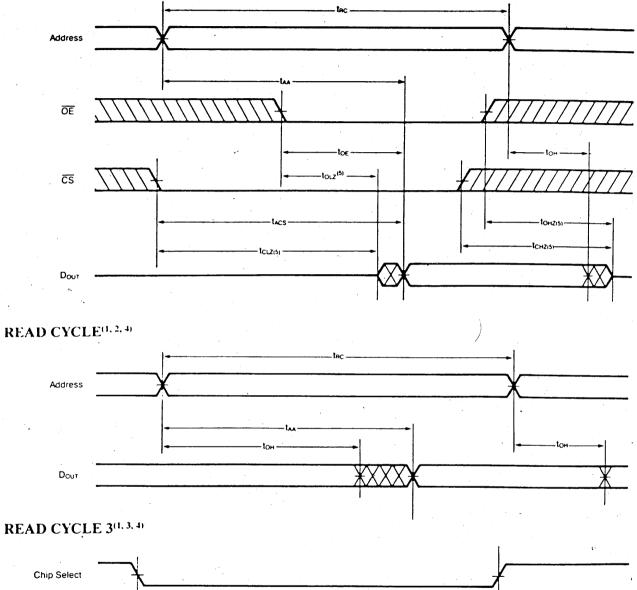

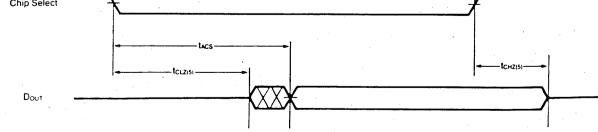

<sup>13</sup>Consult system timing diagram.

<sup>14</sup>Measured from address change to 90% point of -2V to + 2V output LOW-to-HIGH transition.

<sup>16</sup>Measured from address change to 10% point of + 2V to - 2V output HIGH-to-LOW transition.

<sup>16</sup>Measured from 50% transition point of ENABLE input to 90% transition of 0V to -2V output.

<sup>17</sup>Measured from 50% transition point of ENABLE input to 10% transition of +2V to 0V output.

<sup>18</sup>Measured while switching between two grounded channels.

<sup>19</sup>Maximum power dissipation is a package-dependent parameter related to the following typical thermal impedances:

- 16-Pin Ceramic  $\theta_{IA} = 87^{\circ}$ C/W;  $\theta_{IC} = 25^{\circ}$ C/W

- 20-Pin LCC  $\theta_{JA}$ 74°C/W; θ<sub>1C</sub> 10°C/W

Specifications subject to change without notice.

#### **EXPLANATION OF TEST LEVELS**

Test Level I 100% production tested. 100% production tested at  $+25^{\circ}$ C, and sample tested at specified temperatures. Test Level II \_ Test Level III Sample tested only. ---Parameter is guaranteed by design and characterization testing. Test Level IV Test Level V Parameter is a typical value only. Test Level VI All devices are 100% production tested at + 25°C. 100% production tested at temperature extremes for military temperature devices; sample tested at temperature extremes for commercial/industrial devices.

#### **EXPLANATION OF GROUP A MILITARY SUBGROUPS**

| Subgr | oupl –   | Static tests at +25°C.                                       |

|-------|----------|--------------------------------------------------------------|

| 1     |          | (5% PDA calculated against Subgroup 1 for high-rel versions) |

| Subgr | oup 2 –  | Static tests at maximum rated temperature.                   |

| Subgr | ойр3 –   | Static tests at minimum rated temperature.                   |

| Subgr | овр4 –   | Dynamic tests at + 25°C.                                     |

| Subgr | oup5 –   | Dynamic tests at maximum rated temperature.                  |

| Subgr | oup6 –   | Dynamic tests at minimum rated temperature.                  |

| Subgr | oup7 -   | Functional tests at + 25°C.                                  |

| Subgr | oup 8 -  | Functional tests at maximum and minimum rated temperatures.  |

| Subgr | oup9 -   | Switching tests at + 25°C.                                   |

| Subgr | oup 10 - | Switching tests at maximum rated temperature.                |

| Subgr | oup11    | Switching tests at minimum rated temperature.                |

| Subgr | oup 12 - | Periodically sample tested.                                  |

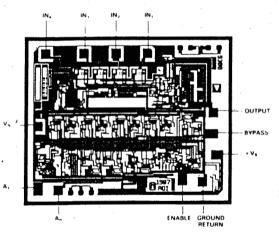

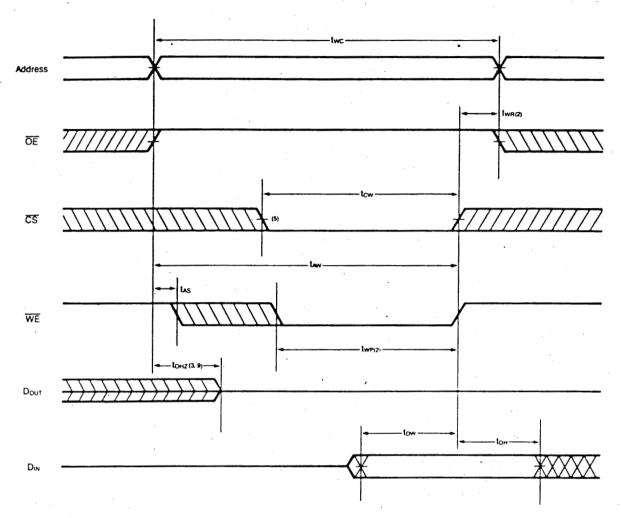

#### AD9300 BURN-IN DIAGRAM

D.

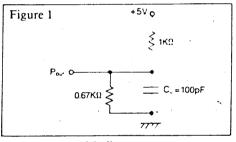

#### SUGGESTED LAYOUT OF AD9300 PC BOARD

METALIZATION PHOTOGRAPH

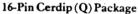

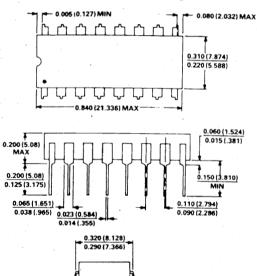

#### **MECHANICAL INFORMATION**

| Die Dimensions           | $84 \times 104 \times 18$ (max) mils |

|--------------------------|--------------------------------------|

| Pad Dimensions           | $4 \times 4$ (min) mils              |

| Metalization             | Aluminum                             |

| Backing                  | None                                 |

| Substrate Potential      | $-V_s$                               |

| Passivation              | Oxynitride                           |

| Die Attach               |                                      |

| Bond Wire 1.25 mil, Alum | inum; Ultrasonic Bonding             |

| or 1 mil                 | , Gold; Gold Ball Bonding            |

(Bottom View – Not to Scale) Component Side Should be Ground Plane

**OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

<u>0.015 (0.381)</u> 0.008 (0.203)

NOTES: LEAD NO. 1 IDENTIFIED BY DOT OR NOTCH. LEADS ARE SOLDER-DIPPED OR TIN-PLATED KOVAR OR ALLOY 42.

#### 20-Pin LCC (E) Package

-4--

#### FUNCTIONAL DESCRIPTION

| $IN_1 - IN_4$  | Four analog input channels.                                                 |

|----------------|-----------------------------------------------------------------------------|

| GROUND         | Analog input shielding grounds, not internally connected. Connect each to   |

|                | external low-impedance ground as close to device as possible.               |

| A <sub>0</sub> | One of two TTL decode control lines required for channel selection. See     |

|                | Logic Truth Table.                                                          |

| A <sub>1</sub> | One of two TTL decode control lines required for channel selection. See     |