# PROJECT REPORT

<u>ON</u>

## DESIGN AND FABRICATION OF HIGH BANDWIDTH POTENTIOSTAT AND GALVANOSTAT FOR ELECTROCHEMICAL STUDIES

(SEPT.15, 1998 TO DEC. 20, 1998)

By

## Jagat Shakya

Assit. Lecturer of Physics Central Department of Physics Tribhuvan University, Kirtipur, Kathmandu, Nepal

> **RAMAN RESEARCH INSTITUTE** BANCONCOLO 80 Under the supervision and rebrU

Prof. V. Lakshminarayanan Raman Research Institute, Bangalore-560080, India

## <u>Acknowledgements</u>

I would like to express my sincere thanks to the Director, Raman Research Institute for kindly permitting me to work in the Institute and for providing the necessary facilities to carry out this project. I am grateful to Prof. G. S. Ranganath, Dean of Research, who invited me to visit the institute. I am also grateful to Prof. Shekhar Gurung, Head of Department, Central Department of Physics, Tribhuvan University, Kathmandu, Nepal for kindly giving me permission to visit RRI.

No words will be sufficient to express my gratitude to Prof. V. Lakshminarayanan, Raman Research Institute, who encouraged me all the way. His experienced and invaluable guidance always led me towards right way to deal with the problems. I would like to thank R. Subramanian, Ph.D. scholar at Raman Research Institute, who taught me the ABC... of electrochemical system and helped me through out the project.

Thanks are due to Mr. N. Ravi Shankar of Electrochemistry Laboratory RRI, Mr. Mani and Mr. Gokul of RRI workshop who helped me in fabricating the instrument. Thanks are also due to all the members of electronics laboratory for their help in every respect. I also thank to Mr. Radhakrisnan, LC Department RRI for his kind help during the project.

I am very much impressed by the hospitality of RRI and I thank all the staff members of administration and canteen. The help of Surajit, Udaya, Ujjal, Vishwanath, Subashree, Amarnath, Giridhar, Amitabh and all other friends at RRI will always remain in my mind as a symbol of good friendship.

> en Alexandrea Alexandrea

Jagat Shakya

## **Contents**

| 1. | Introduction<br>Electrochemical cell and its electrical equivalent circuits<br>Electrochemistry a linear system? | 1<br>2<br>6          |

|----|------------------------------------------------------------------------------------------------------------------|----------------------|

| 2. | Operational amplifier<br>Ideal op-amp model<br>Op-amp specification<br>Some circuits using op-amps               | 10<br>12<br>18<br>21 |

| 3. | Potentiostats and galvanostats<br>Current booster<br>Measurement of cell current<br>Galvanostat                  | 24<br>30<br>34<br>37 |

| 4. | Design                                                                                                           | 38                   |

| 5. | EIS studies using potentiostat                                                                                   | 42                   |

| 6. | Conclusion                                                                                                       | 47                   |

| 7. | References                                                                                                       | 49                   |

\*

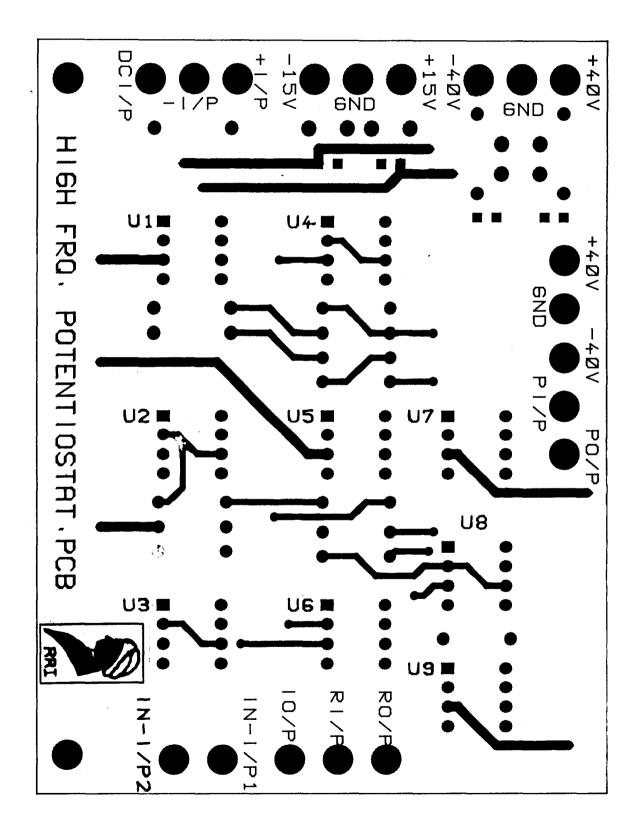

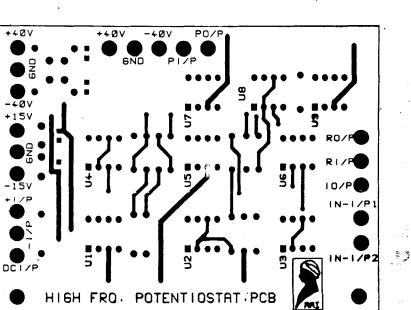

| Appendix 1 | PCB layout            |

|------------|-----------------------|

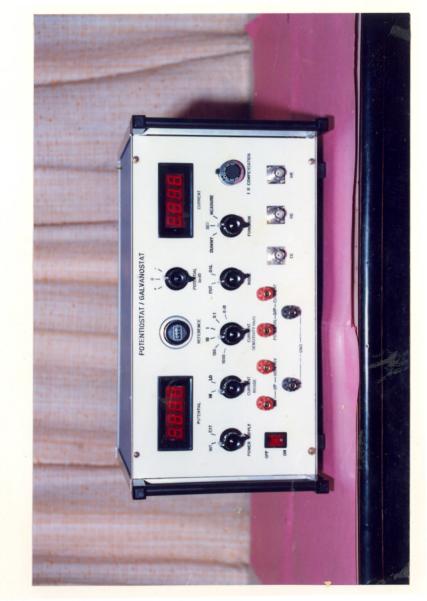

| Appendix 2 | Picture of Instrument |

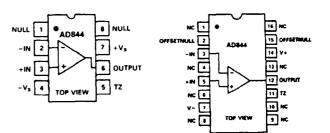

| Appendix 3 | Datasheet of AD844    |

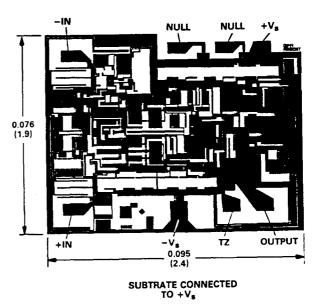

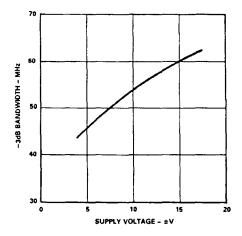

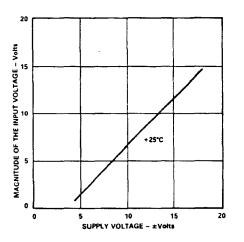

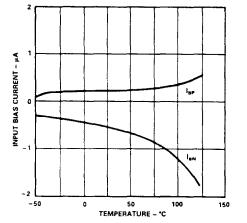

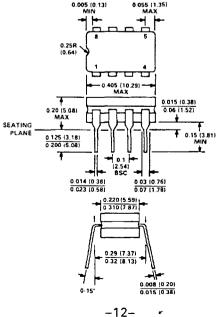

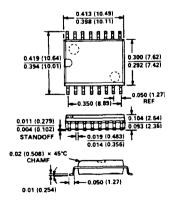

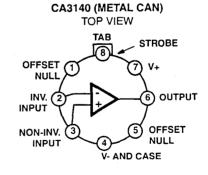

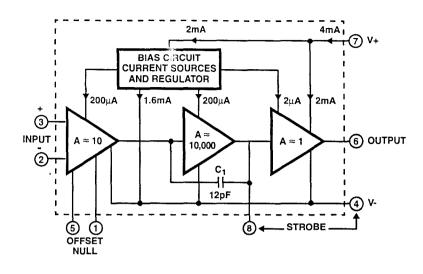

| Appendix 4 | Datasheet of CA3140   |

| Appendix 5 | Datasheet of PB58     |

## 1. Introduction

Potentiostat and Galvanostat are among the most useful device used in Electrochemistry specially in Electrochemical Impedance Spectroscopy (EIS). Electrochemical experiments such as potentiometry, amperometry, diferential capacitance mesurement, impedance measurement, voltametry, coulometry etc. are done using Potentiostat / Galvanostat. One of the most useful application of potentiostat in material science is corrosion measurement. All these and other electrochemical methods requires controlling and measuring the electrical parameters of an electrode reaction, which is achieved by these devices.

Electrochemical experiments are done either by potential control method or by current control method. Potentiostat is used in potential controlled method to maintain the constant potential, between reference electrode RE and working electrode WE in three electrode electrochemical system, irrespective of changes in the impedance of the cell due to chemical reactions taking place in the cell. Similarly galvanostat is used in current controlled method which maintains constant current in the system irrespective of the changes in impedance of cell. Even though there are already so many researches had been done and a large number of literatures had been published in different era of time since the invention of vaccum tube electronics and many companies are producing fully computer controlled potentiostat, an attempt has been made to design and fabricate "relatively" high frequency high power potentiostats / galvanostats have complicated circutary, since they are made for general purpose, and poor high frequency response, though they are precious at low frequency. Secondly, such shortcomings are eliminated in some commercially available potentiostat but these are more expensive.

The high frequency control system is required in many electrochemical experiment, for example if the double layer capacitance (Cdl) typically is low and so as the uncompensated resistance (Ru) and electrode electrolyte interface resistance (Rt), in Randles Cell, then one must go to high frequency. Such type of experiments has also been performed for testing the performance of device built. Similarly mass transfer reaction like experiments require high current which is to be controlled with in certain limit of precision. The electrical parameter of the electrode can be controlled through a wide range of frequency band (0 to 1 MHz) and with a large current (about 1 ampere) using this "home made" potentiostat.

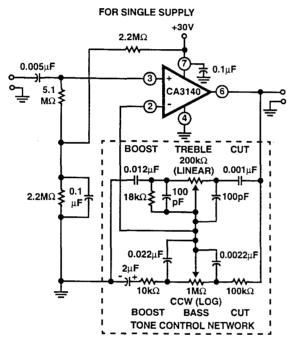

The whole instrument is based upon semiconductor electronics and the circuits have been kept as simple as possible. Since it is required to have some idea of cells and their electrical equivalent model, briefly they are introduced here. Operational amplifier is the main building block of the instrument, it's better to have ideas of operational amplifiers and their internal structure and mode of operations. But it is not possible here to discuss all the internal structure of the op-amp so it is considered as "black box amplifier" and its mode of operation are discussed here. The choice of operational amplifier has been done according to the specification provided by manufacturer. We are briefly discussing about AD844, CA3140 high frequency op-amps and PB58A high frequency high power op-amp.

## **1.1 Electrochemical cell and its electrical equivalent circuits**

In electrochemistry some conducting materials called electrode are used either to study their properties or to measure potential or to supply current. The electrodes are immersed in an electrolyte (an electrically conductive solution). The collection of the electrodes, the solution and the container holding the solution are referred to as an electrochemical cell. The chemical reactions inside cell produces some potential difference between electrodes and electrolyte so current may flow in the cell. Generally two electrodes are required to complete the circuit. But in potential controlled system the potential of one electrode must be controlled with respect to some reference, so that three-electrode system is used in such cases. A potentiostat requires an electrochemical cell with three electrodes.

The three electrodes are called Working Electrode (WE), Reference Electrode (RE) and Counter (or Auxiliary) Electrode (CE).

#### **Working Electrode**

Working electrode is the sample understudy in an electrochemical system. The working electrode can be bare metal or coated. More generally, the electrochemical reactions being studied occur at the working electrode.

#### **Reference Electrode**

The reference electrode is used in measuring the working electrode potential. A reference electrode should have a constant electrochemical potential as long as no current flows through it. The most common lab references are the Saturated Calomel Electrode (SCE) and the Silver/Silver Chloride (Ag /AgCl) electrodes. In field probes, a pseudo-reference (a piece of the working electrode material) is often used.

#### **Counter or Auxiliary Electrode**

The counter electrode is a conductor that completes the cell circuit. The auxiliary (counter) electrode in lab cells is generally an inert conductor like platinum or graphite. In field probes it's generally another piece of the working electrode material. The current that flows into the solution via the working electrode leaves the solution via the auxiliary electrode.

A potentiostat is an electronic device that controls the voltage difference between a working electrode and a reference electrode. Both electrodes are contained in a electrochemical cell. The potentiostat implements this control by injecting current into the cell through an auxiliary electrode. In almost all applications, the potentiostat measures the current flow between the working and auxiliary electrodes. The controlled variable in a potentiostat is the cell potential and the measured variable is the cell current.

#### AC Circuit Theory and Representation of Complex Impedance Values

#### Impedance definition: concept of complex impedance

Electrical resistance is the ability of a circuit element to resist the flow of electrical current. Ohm's law (Equation 1-1) defines resistance in terms of the ratio between voltage E and current I.

While this is a well-known relationship, its use is limited to only one circuit element - the ideal resistor. An ideal resistor has several simplifying properties:

· It follows Ohm's Law at all current and voltage levels.

· Its resistance value is independent of frequency.

• AC current and voltage signals though a resistor is in phase with each other.

The real world contains circuit elements that exhibit much more complex behaviour. These elements force us to abandon the simple concept of resistance. In its place we use impedance, which is a more general circuit parameter. Like resistance, impedance is a measure of the ability of a circuit to resist the flow of electrical current. Unlike resistance, impedance is not limited by the simplifying properties listed above.

Electrochemical impedance is usually measured by applying an AC potential to an electrochemical cell and measuring the current through the cell. Suppose that we apply a sinusoidal potential excitation. The response to this potential is an AC current signal, containing the excitation frequency and it's harmonics. This current signal can be analysed as a sum of sinusoidal functions (a Fourier series).

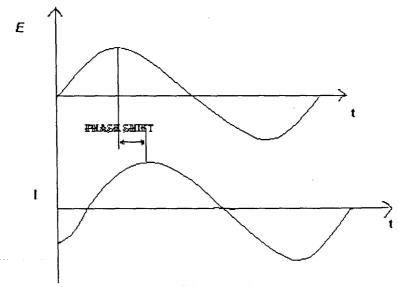

Electrochemical Impedance is normally measured using a small excitation signal. This is done so that the cell's response is pseudo-linear. In a linear (or pseudo-linear) system, the current response to a sinusoidal potential will be a sinusoid at the same frequency but shifted in phase. See Figure 1-1

Figure 1-1 Sinusoidal Current Response in a Linear System

The excitation signal, expressed as a function of time, has the form  $E(t) = E_o \cos(\omega t)$  .....1.2

E(t) is the potential at time tr Eo is the amplitude of the signal, and w is the radial frequency. The relationship between radial frequency w (expressed in radians/second) and frequency f (expressed in hertz) is:

$\omega = 2\pi f \dots 1.3$

In a linear system, the response signal,  $I_t,$  is shifted in phase  $\phi$  and has a different amplitude,  $I_0:$

$I(t) = I_o \cos(\omega t - \phi) \dots 1.4$

An expression analogous to Ohm's Law allows us to calculate the impedance of the system as:

The impedance is therefore expressed in terms of a magnitude,  $Z_0$ , and a phase shift,  $\phi$ .

If we plot the applied sinusoidal signal on the X-axis of a graph and the sinusoidal response signal I(t) on the Y-axis, an oval called a "Lissajous figure" is plotted. Analysis of Lissajous figures on oscilloscope screen was the accepted method of impedance measurement prior to the availability of lock-in amplifiers and frequency response analyzers.

Using Eulers relationship,

$\exp(j\phi) = \cos \phi + j \sin \phi$  The impedance is then represented as a complex number,

$Z = Zo \exp (i\phi) = Zo (\cos \phi + i \sin \phi).....1.6$

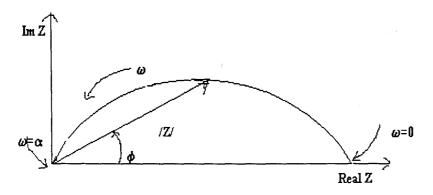

In Equation (1-6) the expression for Z(w) is composed of a real and an imaginary part. If the real part is plotted on the Z axis and the imaginary part on the Y axis of a chart, we get a "Nyquist plot". See Figure 1-2. Notice that in this plot the y-axis is negative and that each point on the Nyquist plot is the impedance at one frequency.

Figure 1-2 Nyquist Plot with Impedance Vector

\*\*

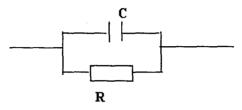

Figure 1-2 has been annotated to show that low frequency data are on the right side of the plot and higher frequencies are on the left. This is true for EIS data where impedance usually falls as frequency rises (this is not true of all circuits). On the Nyquist plot the impedance can be represented as a vector of length |Z|. The angle between this vector and the x-axis is  $\phi$ , where  $\phi = \arg(Z)$ . Nyquist plots have one major shortcoming. When we look at any data point on the plot, we cannot tell what frequency was used to record that point. The Nyquist plot in Figure 1-2 results from the electrical circuit of Figure 1-3 The semicircle is characteristic of a single "time constant". Electrochemical Impedance plots often contain several time constants. Often only a portion of one or more of their semicircles is seen.

Figure 1-3 Simple Equivalent Circuit with One Time Constant

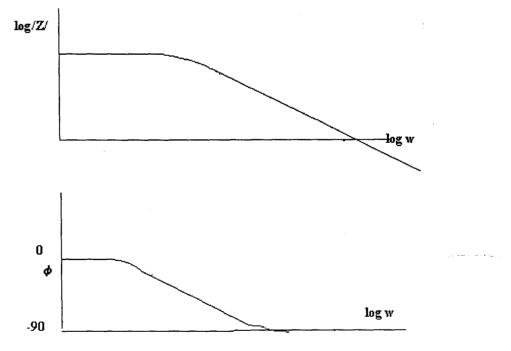

Another popular presentation method is the "Bode plot". The impedance is plotted with log frequency on the x-axis and both the absolute value of the impedance (|Z| = Z0) and phase-shift on the y-axis. The Bode plot for the electric circuit of Figure 1-3 is shown in Figure 1-4. Unlike the Nyquist plot, the Bode plot explicitly shows frequency information.

Figure 1-4 Bode Plot with One Time Constant

#### 1.2 <u>Electrochemistry - A Linear System?</u>

Electrical circuit theory distinguishes between linear and non-linear systems (circuits). Impedance analysis of linear circuits is much easier than analysis of non-linear ones. The following definition of a linear system is taken from Signals and Systems by Oppenheim and Willsky:

A linear system ... is one that possesses the important property of superposition: If the input consists of the weighted sum of several signals, then the output is simply the superposition, that is, the weighted sum, of the responses of the system to each of the signals. Mathematically, let  $y_1(t)$  be the response of a continuous time system to  $x_1(t)$  and let  $y_2(t)$  be the output corresponding to the input  $x_2(t)$ . Then the system is linear if:

1) The response to  $x_1(t) + x_2(t)$  is  $y_1(t) + y_2(t)$

2) The response to  $ax_1(t)$  is  $ay_1(t) \dots$

For a potentiostated electrochemical cell, the input is the potential and the output is the current. Electrochemical cells are not linear! Doubling the voltage will not necessarily double the current. However, electrochemical systems can be pseudo-linear. When we look at a small enough portion of a cell's current versus voltage curve, it seems to be linear. In normal EIS practice, a small (1 to 10 mV) AC signal is applied to the cell. The signal is small enough to confine ourselves to a pseudo-linear segment of the cell's current versus voltage curve. The cell's non-linear response to the DC potential is not measured because in EIS only the cell current at the excitation frequency is measured. If the system is non-linear, the current response will contain harmonics of the excitation frequency.

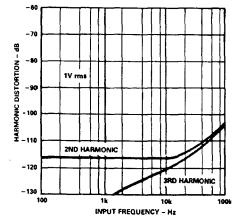

Some researchers have made use of this phenomenon. Linear systems should not generate harmonics, so the presence or absence of significant harmonic response allows one to determine the system's linearity. Other researchers have intentionally used larger amplitude excitation potentials. They use the harmonic response to estimate the curvature in the cell's current voltage curve.

#### Steady State Systems

Measuring an EIS spectrum takes time (often many hours). The system being measured must be at a steady state throughout the time required to measure the EIS spectrum. A common cause of problems in EIS measurements and their analysis is drift in the system being measured. In practice a steady state can be difficult to achieve. The cell can change through adsorption of solution impurities, growth of an oxide layer, build up of reaction products in solution, coating degradation, temperature changes, to list just a few factors. Standard EIS analysis tools may give wildly inaccurate results on a system that is not at a steady state.

#### **Electrical Circuit Elements**

EIS data is commonly analysed by fitting it to an equivalent electrical circuit model. Most of the circuit elements in the model are common electrical elements such as

**\***\*\*

resistors, capacitors, and inductors. To be useful, the elements in the model should have a basis in the physical electrochemistry of the system. As an example, most models contain a resistor that models the cell's solution resistance.

Some knowledge of the impedance of the standard circuit components is therefore quite useful. The common circuit elements are given, the equation for their current versus voltage relationship, and their impedance

| Component | Current Vs Voltage | Impedance         |  |

|-----------|--------------------|-------------------|--|

| resistor  | E= IR              | Z = R             |  |

| inductor  | E = L di/dt        | $Z = j\omega L$   |  |

| capacitor | I = C dE/dt        | $Z = 1/j\omega C$ |  |

Common Electrical Elements

Notice that the impedance of a resistor is independent of frequency and has only a real component. Because there is no imaginary impedance, the current through a resistor is always in phase with the voltage.

The impedance of an inductor increases as frequency increases. Inductors have only an imaginary impedance component. As a result, an inductor's current is phase shifted 90 degrees with respect to the voltage.

The impedance versus frequency behaviour of a capacitor is opposite to that of an inductor. A capacitor's impedance decreases as the frequency is raised. Capacitor also has only an imaginary impedance component. The current through a capacitor is phase shifted -90 degrees with respect to the voltage.

#### Serial and Parallel Combinations of Circuit Elements

Very few electrochemical cells can be modelled using a single equivalent circuit element. Instead, EIS models usually consist of a number of elements in a network. Both serial and parallel combinations of elements occur. Fortunately, there are simple formulas that describe the impedance of circuit elements in both parallel and series combinations.

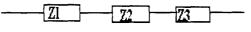

Figure 1-5 Impedances in Series

For linear impedance elements in series the equivalent impedance can be calculated as

$$Zeq = Z_1 + Z_2 + Z_3$$

.....(1-7)

Figure 1-6 Impedances in Parallel For linear impedance elements in parallel the equivalent impedance can be calculated as

#### Physical Electrochemistry and Equivalent Circuit Elements

#### **Electrolyte Resistance**

Solution resistance is often a significant factor in the impedance of an electrochemical cell. A modern 3-electrode potentiostat compensates for the solution resistance between the counter and reference electrodes. However, any solution resistance between the reference electrode and the working electrode must be considered when the cell is modelled.

The resistance of an ionic solution depends on the ionic concentration, type of ions,  $$\rm Rest.$

temperature and the geometry of the area in which current is carried. In a bounded area with area A and length 1 carrying a uniform current the resistance is defined as:

where r is the solution resistivity. The conductivity of the solution, k, is more commonly used in solution resistance calculations. Its relationship with solution resistance is:

$$R = \frac{l}{kA} \Longrightarrow k = \frac{l}{RA}....(1-10)$$

Standard chemical handbooks list k values for specific solutions. For other solutions, one can calculate k from specific ion conductances. The units for k are Siemens per meter (S/m). The Siemen is the reciprocal of the ohm, so 1 S = 1/ohm.

Unfortunately, most electrochemical cells do not have uniform current distribution through a definite electrolyte area. The major problem in calculating solution resistance therefore concerns determination of the current flow path and the geometry of the electrolyte that carries the current. Fortunately, we don't usually calculate solution resistance from ionic conductances. Instead, it is found when we fit a model to experimental EIS data.

#### **Double Layer Capacitance**

A electrical double layer exists at the interface between an electrode and its surrounding electrolyte. This double layer is formed as ions from the solution "stick on" the electrode surface. Charges in the electrode are separated from the charges of these ions. The separation is very small, on the order of angstroms. Charges separated by an insulator form a capacitor. On a bare metal immersed in an electrolyte, you can estimate that there will be approximately  $30 \ \mu F$  of capacitance for every cm<sup>2</sup> of electrode area. The value of the double layer capacitance depends on many variables including electrode potential, temperature, ionic concentrations, types of ions, oxide layers, electrode roughness, impurity adsorption, etc.

Besides these there are Polarisation resistance, charge transfer resistance diffusion impedance (Warburg impedance), coating capacitance etc

### Simple Equivalent Circuit Model

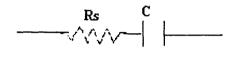

#### Model #1 - A Purely Capacitive Coating

A metal covered with an undamaged coating generally has a very high impedance. The equivalent circuit for such a situation is in Figure 1-7.

Figure 1-7

Purely Capacitive Coating The model includes a resistor (due primarily to the electrolyte) and the coating capacitance in series.

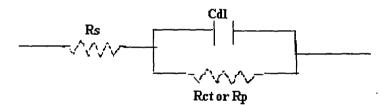

#### Model #2 -- Randles Cell

The Randles cell is one of the simplest and most common cell models. It includes a solution resistance, a double layer capacitor and a charge transfer or polarisation resistance. In addition to being a useful model in its own right, the Randles cell model is often the starting point for other more complex models. The equivalent circuit for the

Randles cell is shown in Figure 1-8. The double layer capacitor is in parallel with the impedance due to the charge transfer reaction.

#### Figure 1-8 Randles Cell Schematic Diagram

There are other complex and more generalised models for cells, but being simple and useful we consider here this cell model throughout our study

## 2 **Operational amplifiers**

#### 2.1 Introduction

The term operational amplifier, abbreviated op amp, was coined in the 1940s to refer to a special kind of amplifier that, by proper selection of external components, can be configured to perform a variety of mathematical operations. Early op amps were made from vacuum tubes consuming lots of space and energy. Later op-amps were made smaller by implementing them with discrete transistors. Today, op amps are monolithic integrated circuits, highly efficient and cost effective.

Almost all of our present work is based upon the op-amp so the basic idea behind such integrated circuit op-amp (IC op-amp) is discussed along with few elementary circuits, which are used in our instrument. It is not to be mentioned that at present semiconductor devices play indispensable roll in modern tecnology. Op-amp is one of such small linear device, which forms heart of many sophisticated electronic devices. One op-amp IC chip may contain thousands of transistors diodes capacitors and resistors altogether. The internal structure of Op-amp varies according to their special purpose of use, and different part numbers given by manufacturers identifies them. So it is not possible here to discuss about internal structure of all op-amp ,but they shear some common mechanism, like all of them have at least one transistorised differential amplifier (this circuit contains two transistors having two input and two outputs, the output voltage of this circuit is the difference between its two inputs) and many transistor amplifiers inside it ,to meet the properties of ideal op-amp.

#### **Amplifier Basics**

en en an an<del>na a</del>t et

Before jumping into op amps, lets take a minute to review some amplifier fundamentals. An amplifier has an input port and an output port. In a linear amplifier, output signal = A x input signal, where A is the amplification factor or gain. Depending on the nature of input and output signals, we can have four types of amplifier gain: # Voltage (voltage out/voltage in)

- # Current (current out/current in)

- # Transresistance (voltage out/current in)

- # Transconductance (current out/voltage in)

Since most op amps are voltage amplifiers, we will limit our discussion to voltage amplifiers.

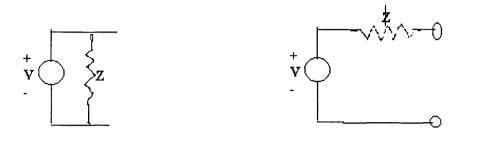

#### **Thevenin's and Norton's Theorems**

The input source to an amplifier may be represented either by a series circuit as in fig 1.2 or by a parallel network. This result is a special case of Thevenin and Norton's theorems. <u>Thevenin's theorem</u> states that "any two terminal linear network may be replaced by a voltage source equal to the open circuit voltage between the terminals in series with output impedance seen at this port".

In fig 2.1, V represents the open circuit voltage and Z is the impedance between two terminals. To find Z all independent voltage sources are short-circuited and all independent current sources are open-circuited and the impedance is "seen from outside in".

Fig 2.1

Norton's Theorem

The dual of Thevenin's theorem is Norton's theorem which states that "any two terminal linear network may be replaced by a current source equal to the short circuited current between the terminals in parallel with the output impedance seen at this port"

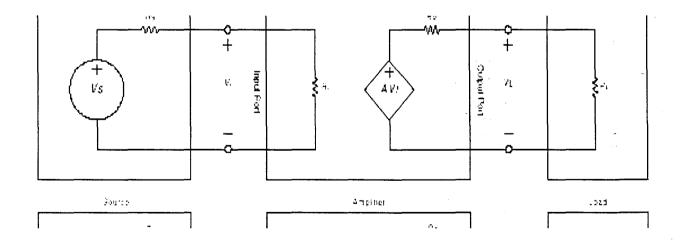

Thevenin's theorem can be used to derive a model of an amplifier, reducing it to the appropriate voltage sources and series resistances. The input port plays a passive role, producing no voltage of its own, and its Thevenin equivalent is a resistive element, Ri. The output port can be modelled by a dependent voltage source, AVi, with output resistance, R<sub>o</sub>. To complete a simple amplifier circuit, we will include an input source and impedance, VS and RS, and output load, RL. Figure 1 shows the Thevenin equivalent of a simple amplifier circuit.

Figure 2.2 Thevenin Model of Amplifier with Source and Load

It can be seen that we have voltage divider circuits at both the input port and the output port of the amplifier. This requires us to re-calculate whenever a different source and/or load is used and complicates circuit calculations.

#### 2.2 Ideal Op Amp Model

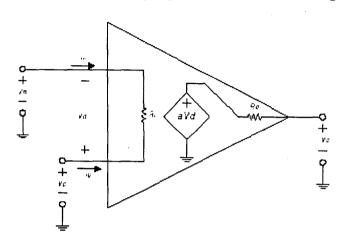

The Thevenin amplifier model shown in Figure 2.2 is redrawn in Figure 2.3 showing standard op amp notation. An op amp is a differential to single-ended amplifier. It amplifies the voltage difference, Vd = Vp - Vn, on the input port and produces a voltage, VO, on the output port that is referenced to ground.

Figure 2.3 Standard Op Amp Notation

We still have the loading effects at the input and output ports as noted above. The ideal op amp model was derived to simplify circuit calculations and is commonly used by engineers in first-order approximation calculations. The ideal model makes three simplifying assumptions:

| # Gain is infinite $a = \alpha$              | (1) |

|----------------------------------------------|-----|

| # Input resistance is infinite $Ri = \alpha$ | (2) |

| # Output resistance is zero $RO = 0$         | (3) |

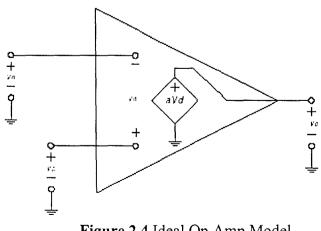

Applying these assumptions to Figure 2 results in the ideal op-amp model shown in Figure 2.4.

\*

Figure 2.4 Ideal Op Amp Model

Other simplifications can be derived using the ideal op amp model:

$$\Rightarrow \mathbf{I}_{n} = \mathbf{I}_{p} = \mathbf{0} \tag{4}$$

Because  $R_i = \alpha$ , we assume  $I_n = I_p = 0$ . There is no loading effect at the input.

$$Vo = a Vd$$

(5) be modeled

Because  $R_0 = 0$  there is no loading effect at the output.

$$\Rightarrow \mathbf{V}\mathbf{d} = \mathbf{0} \tag{6}$$

If the op amp is in linear operation, VO must be a finite voltage. By definition  $V_0 = Vd \ge a$ . Rearranging,  $Vd = V_0 / a$ . Since  $a = \alpha$ ,  $Vd = Vo / \alpha = 0$ . This is the basis of the virtual short concept.

$\Rightarrow$  Common mode gain = 0 (7)

The ideal voltage source driving the output port depends only on the voltage difference across its input port. It rejects any voltage common to Vn and Vp.

| $\Rightarrow$ <b>Bandwidth</b> = $\alpha$ | (8)  |

|-------------------------------------------|------|

| $\Rightarrow$ Slew Rate = $\alpha$        | (9)  |

| No frequency dependencies are assu        | med. |

$$\Rightarrow Drift = 0 \tag{10}$$

There are no changes in performance over time, temperature, humidity, power supply variations, etc.

#### **Non-Inverting Amplifier**

An ideal op amp by itself is not a very useful device since any finite input signal would result in infinite output. By connecting external components around the ideal op amp, we can construct useful amplifier circuits. Figure 2.5 shows a basic op amp circuit, the non-inverting amplifier. The triangular gain block symbol is used to represent an ideal op amp. The input terminal marked with a + (Vp) is called the non-inverting input; – (Vn) marks the inverting input.

Figure 2.5 Non-Inverting Amplifier

13

1.1.1.1

To understand this circuit we must derive a relationship between the input voltage, Vi, and the output voltage, V<sub>0</sub>. Remembering that there is no loading at the input, (2-1)

$$Vp = Vi$$

The voltage at Vn is derived from VO via the resistor network, R1 and R2, so that,

$$V_n = V_o \frac{R_1}{R_1 + R_2} = V_0 b$$

(2-2)

where,  $b = \frac{R_1}{R_1 + R_2}$  (2-3)

The parameter b is called the feedback factor because it represents the portion of the output that is fed back to the input. Recalling the ideal model,  $V_{O} = aVd = a(Vn - Vn)$ (2-4)

Substituting,

$$V_0 = a(V_i - b V_0)$$

(2-5)

and collecting terms yield,

$A = \frac{V_0}{V_i} = \left(\frac{1}{b} \left(\frac{a}{1+\frac{1}{ab}}\right)$  (2-6)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2-5)

(2

R + P

This result shows that the op amp circuit of Figure 2-5 is itself an amplifier with gain A. Since the polarity of Vi and V<sub>0</sub> are the same, it is referred to as a non-inverting amplifier. A is called the close loop gain of the op amp circuit, whereas 'a' is the open loop gain." A final state of the The product 'ab' is called the loop gain. This is the gain a signal would see starting at the second s inverting input and travelling in a clockwise loop through the op amp and the feedback network. าหน้าราวประ

a the second of **Closed Loop Concepts and Simplifications** المتحوص والمحاج المتعلم المحاج المراجع والمنتسب فالراب Substituting  $a = \alpha$ (1) into (2-6) results in,  $A = \frac{1}{b} = 1 + \frac{R_2}{R_1}$ (2-7)

Recalling that in equation (6) we state that Vd, the voltage difference between Vn and Vp, is equal to zero and therefore, Vn = Vp. Still they are not shorted together. Rather there is said to be a virtual short between Vn and Vp. The concept of the virtual short further

simplifies analysis of the non-inverting op amp circuit in Figure 4. Using the virtual short the offense of an concept, we can say that,

.

$$Vn = Vp = Vi$$

(2-8)

Realising that finding Vn is now the same resistor divider problem solved in (2-2) and substituting (2-8) into it, we get,

$$V_{i} = V_{o} \frac{R_{1}}{R_{1} + R_{2}} = V_{0}b$$

(2-9)

Rearranging and solving for A, we get,

$$A = \left(\frac{1}{b}\right) = 1 + \frac{R_1}{R_2}$$

(2-10)

The same result is derived in equation (2-7). Using the virtual short concept reduced solving the non-inverting amplifier, shown in Figure 2.5, to solving a resistor divider network.

#### **Inverting Amplifier**

And Constant Strong of the second

. *K*

Figure 2.6 shows another useful basic op amp circuit, the inverting amplifier. The triangular gain block symbol is again used to represent an ideal op amp. The input terminal, + (Vp), is called the non-inverting input, whereas - (Vn) marks the inverting input. It is similar to the non-inverting circuit shown in Figure 4 except that now the signal is applied to the inverting terminal via R<sub>1</sub> and the non-inverting terminal is grounded.

#### Figure 2.6 Inverting Amplifier

To understand this circuit, we must derive a relationship between the input voltage, Vi and the output voltage, V<sub>0</sub>. Since Vp is tied to ground, Vp = 0 (2-11)

Remembering that there is no current into the input, the voltage at Vn can be found using superposition. First let  $V_0 = 0$ ,

$$V_n = V_i \left(\frac{R_2}{R_1 + R_2}\right)$$

Next let Vi = 0,

(2-12)

$$V_n = V_o \left(\frac{R_1}{R_1 + R_2}\right) \tag{2-13}$$

Combining

$$V_{n} = V_{0} \left( \frac{R_{1}}{R_{1} + R_{2}} \right) + V_{i} \left( \frac{R_{2}}{R_{1} + R_{2}} \right)$$

(2-14)

Remembering equation (14),  $V_0 = aVd = a(Vp - Vn)$ , substituting and rearranging,

$$A = \frac{V_0}{V_i} = 1 - \left(\frac{1}{b} \right) \left(\frac{1}{1 + \frac{1}{ab}}\right)$$

(2-15)

where

$$b = \frac{R_1}{R_1 + R_2}$$

Again we have an amplifier circuit. Because  $b \leq 1$ , the closed loop is an inverting amplifier.

#### **Closed Loop Concepts and Simplifications**

Substituting

$$a = \alpha$$

(1) into (2-15) results in

$$A = 1 - \frac{1}{b} = -\frac{R_2}{R_1} \tag{2-16}$$

Recall that in equation (2-6) we stated that Vd, the voltage difference between Vn and Vp, was equal to zero so that Vn = Vp. Still they are not shorted together. Rather there is said to be a virtual short between Vn and Vp. The concept of the virtual short further simplifies analysis of the inverting op amp circuit in Figure 2.6. Using the virtual short concept, we can say that

$$Vn = Vp = 0$$

(2-17)

In this configuration, the inverting input is a virtual ground. We can write the node equation at the inverting input as

$$\frac{V_n - V_i}{R_1} + \frac{V_n - V_0}{R_2} = 0$$

(2-18)

Since Vn = 0, rearranging, and solving for A we get

$$A = 1 - \frac{1}{b} = -\frac{R_2}{R_1} \tag{2-19}$$

The same result is derived more easily than in (2-16). Using the virtual short (or virtual ground) concept reduced solving the inverting amplifier, shown in Figure 2.6, to solving a single node equation.

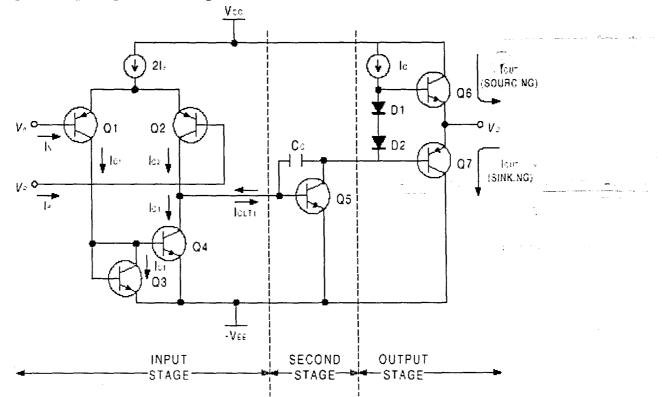

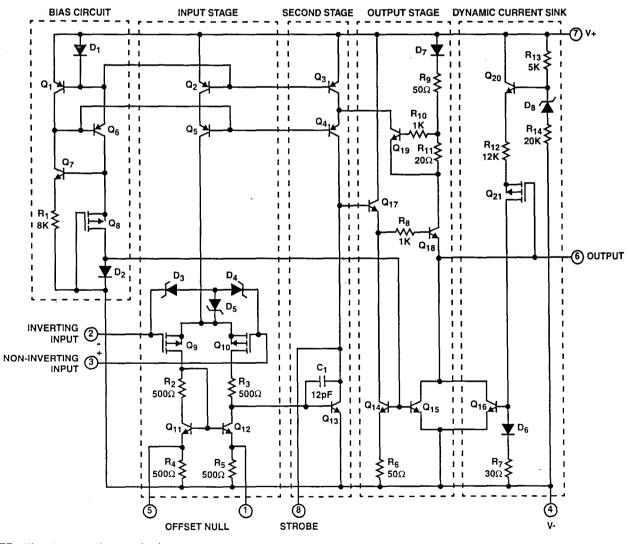

#### Simplified Op Amp Circuit Diagram

Real op amps are not ideal. They have limitations. To understand and discuss the origins of these limitations, see the simplified op amp circuit diagram shown in Figure 2.7.

Although simplified, this circuit contains the three basic elements normally found in op amps:

#### # Input stage

#### # Second stage

# Output stage

The function of the input stage is to amplify the input difference, Vp - Vn, and convert it to a single-ended signal. The second stage further amplifies the signal and provides frequency compensation. The output stage provides output drive capability.

#### **Input Stage**

Symmetry of the input stage is key to its operation. Each transistor pair, Q1-Q2 e de de and Q3-Q4, is matched as closely as possible. Q3 is diode connected. This forces the collector current in Q3 to equal  $I_{C1}$ . The base-emitter junctions of Q3 and Q4 are in Q3parallel so they both see the same V<sub>BE</sub>. Because Q4 is matched to Q3, its collector current is also equal to I<sub>C1</sub>. This circuit is called a current mirror. Current source 2I<sub>E</sub> is divided between Q1 and Q2. This division depends on the input voltages, Vp and Vn. When Vp is more positive than Vn, Q1 carries more current than Q2, and I<sub>C1</sub> is larger than  $I_{C2}$ . The current mirror action of Q3-Q4 causes  $I_{out1}$  to flow into the collectorcollector junction of Q2-Q4. When Vn is more positive than VP, Q2 carries more current than Q1 and I<sub>C2</sub> is larger than I<sub>C1</sub>. The current mirror action of Q3-Q4 causes I<sub>OUT1</sub> to flow out of the collector-collector junction of Q2-Q4. Ioutl is the single-ended signal out of the same service and first stage and is proportional to the differential input, Vp@Vn?and is proportional to the differential

$I_{out1} = gm_1(Vp - Vn).$

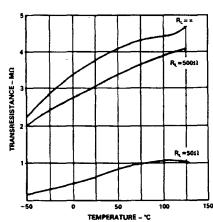

The term gm<sub>1</sub> is called the *transconductance* of the input stage. The input stage is a transconductance amplifier.

#### Second Stage

The second stage converts I<sub>out1</sub> into a voltage and provides frequency compensation. If I<sub>out1</sub> flows into the collector-collector junction of Q2-Q4, the second stage output voltage is driven positive. If Ioutl flows out of the collector-collector junction of Q2-Q4, the second stage output voltage is driven negative. The second stage is a *transresistance* amplifier. The capacitor,  $C_{\rm C}$ , in the second stage provides internal frequency compensation. It causes the gain to role off as the frequency increases. Without C<sub>c</sub>, external compensation is required to prevent the op amp from oscillating in most applications.

#### **Output Stage**

The output stage is a typical class AB, push-pull amplifier. The emitter follower configuration of Q6 and Q7 provides current drive for the output load, with unity voltage gain. The output stage is a current amplifier.

#### 2.3 Op Amp Specifications

· · · · · · · · - —

Op amp circuits at moderate gain and frequency generally has very good agreement between actual performance and ideal performance. As gain and/or frequency is increased, however, certain op amp limitations come into play that effect circuit performance. In theory, with proper understanding of the internal structures and processes used to fabricate an op amp, we could calculate these effects. Thankfully this is not necessary, as manufacturers provide this information in data sheets. Proper interpretation of data sheet specifications is required when selecting an op amp for an application.

a constant a constant a constant constant

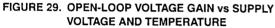

#### (A<sub>V</sub>)Large-signal voltage amplification

The ratio of the peak-to-peak output voltage swing to the change in input voltage state output of required driving the output.

## (Avp.) Differential voltage amplification

producing it with the common-mode input voltage held constant.

#### Unity gain bandwidth

The range of frequencies within which the open-loop voltage amplification is the second greater that unity. ina. La selesia en tragan la selesia en al

#### Input capacitance

The capacitance between the input terminals with either input grounded. जन्महारी जन्म नामक **नामक राषिक**

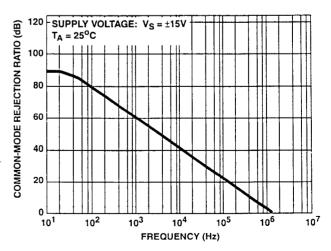

#### CMRR (Common-mode rejection ratio)

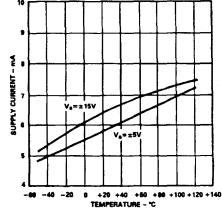

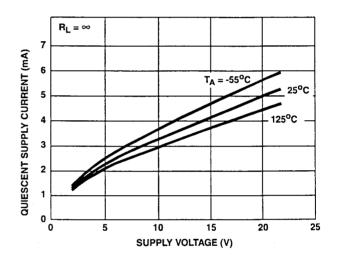

The ratio of differential voltage amplification to common-mode voltage d voltage a amplification. (This is measured by determining the ratio of a change in input commonand the second particular mode voltage to the resulting change in input offset voltage.) Supply current

The current into the  $V_{CC}$ + or  $V_{CC}$ - terminal of an integrated circuit.

#### IIB (Input bias current)

The average of the currents into the two input terminals with the output at the specified level.

#### IIO (Input offset current)

The difference between the currents into the two input terminals with the output at the specified level.

#### IOS (Short-circuit output current)

The maximum output current available from the amplifier with the output shorted to ground, to either supply, or to a specified point.

#### PD(Total power dissipation)

The total dc power supplied to the device less any power delivered from the device to a load.

#### Ri (Input resistance)

The resistance between the input terminals with either input grounded. **Rid (Differential input resistance)**

The small-signal resistance between two ungrounded input terminals.

#### **Ro Output resistance**

The resistance between an output terminal and ground.

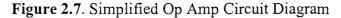

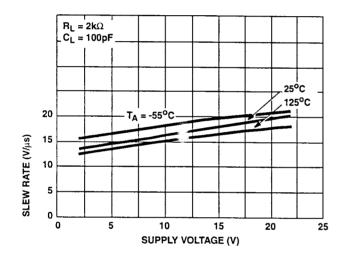

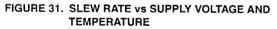

#### SR (Slew rate)

The average time rate of change of the closed-loop amplifier output voltage for a step-signal input.

#### tr (Rise time)

The time required for an output voltage step to change from 10% to 90% of its final value. and the second

#### Total response time

The time between a step-function change of the input signal and the instant at which the magnitude of the output signal reaches, for the last time, a specified level range  $(\pm V)$  containing the final output signal level.

#### V<sub>I</sub> (Input voltage range)

The range of voltage that if exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational and the exceeded at either input may cause the operational at exceeded at either input may cause the operational at exceeded at either input may cause the operational at exceeded at either input may cause the operational at exceeded at either input may cause the operational at exceeded at either input may cause the operational at exceeded at either input may cause the operational at exceeded at either input may cause the operational at exceeded at either input may cause the operational at exceeded at exce amplifier to cease functioning properly. Tang da in the case of the internation of the A 115 TREPHE COMPLEX SUBLICE

#### V<sub>IO</sub> Input offset voltage

The dc voltage that must be applied between the input terminals to force the quiescent dc output voltage to zero or other level, if specified.

#### VICR Common-mode input voltage range

The range of common-mode input voltage that if exceeded may cause the operational amplifier to cease functioning properly. Differential input voltage

The voltage at the non-inverting input with respect to the inverting input: The manual transmission of the manual transmission of the second s Common-mode input impedance **Common-mode input impedance**

The parallel sum of the small-signal impedance between each input terminal and creund ground.

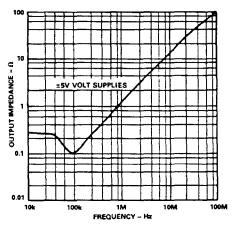

#### Zo Output impedance

The state of the s

이 방법 영화 영화 영화 영화

and the product of the

The small-signal impedance between the output terminal and ground.

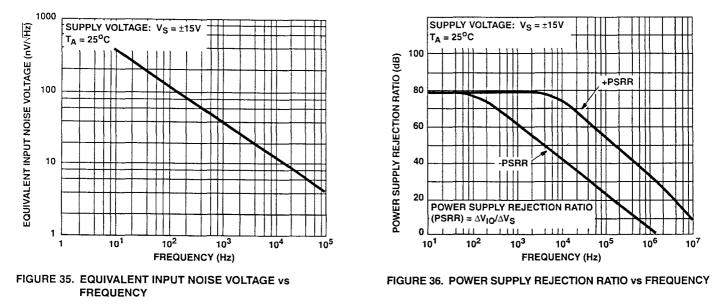

#### THD + N (Total harmonic distortion plus noise)

The ratio of the RMS noise voltage and RMS harmonic voltage of the fundamental signal to the total RMS voltage at the output.

#### **GBW** Gain bandwidth product

The product of the open-loop voltage amplification and the frequency at which it is measured.

#### Slew Rate at Unity Gain

Slew rate, SR, is the rate of change in the output voltage caused by a step input. Its units are V/ms or V/ms. Figure 2.8 shows slew rate graphically. Referring back to Figure 2.7, voltage change in the second stage is limited by the charging and discharging of capacitor C<sub>c</sub>. The maximum rate of change occurs when either side of the differential pair is conducting  $2I_E$ . This is the major limit to slew rate. Essentially,  $SR = 2 I_E / C_C$ . However, there are op amps that work on different principles where this is not true. The requirement to have current flowing in or out of the input stage to change the voltage out of the second stage requires an error voltage at the input anytime the output voltage of an op amp is changing. An error voltage on the order of 120 mV is required for an op amp with a bipolar input to realise full slew rate. This can be as high as 1V to 3V for JFET or MOSFET input. Capacitor,  $C_c$ , is added to make the op amp unity gain stable.

Some op amps come in de-compensated versions where the value of  $C_C$  is reduced. This increases realisable bandwidth and slew rate, but the engineer must ensure the stability of the circuit by other means. To increase slew rate, the bias currents within the op amp are increased.

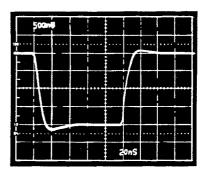

#### Figure 2.8 Slew Rate

#### **Settling Time**

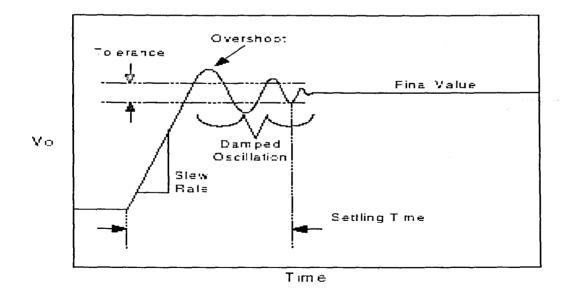

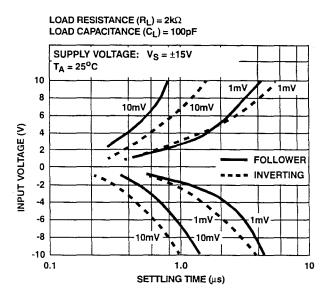

It takes a finite time for a signal to propagate through the internal circuitry of an another second op amp. Therefore, it takes a certain period of time for the output to react to a step change in the input. Also the output normally overshoots the target value, experiences damped oscillation, and settles to a final value. Settling time, t<sub>s</sub>, is the time required for the output voltage to settle to within a specified percentage of the final value given a step input.

#### Figure2.9 SettlingTime

For high frequency application the settling time must be as possible as small.

### 2.4 Some circuits using op-amps

#### **Voltage Follower**

Fig 2.10 shows the op-amp version of emitter follower i.e. voltage follower. Referring to the fig 2.5, it is simply a noninverting amplifier with  $R_1$  infinite and  $R_2$  zero and gain equal to 1. This type of unity gain amplifier is frequently used to isolate the stages for high input impedance and low output impedance and called sometimes as *buffer*

#### Fig 2.10

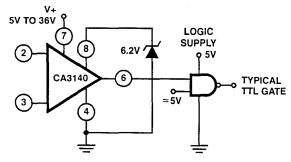

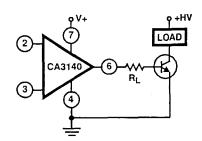

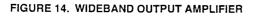

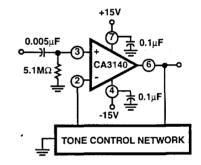

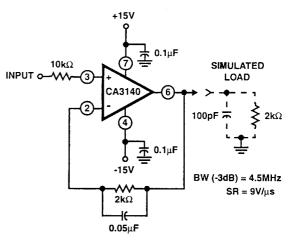

Here in our project CA3140 has been used as voltage follower. Some times one can use a resistor typically 1 k ohm between output to inverting input.

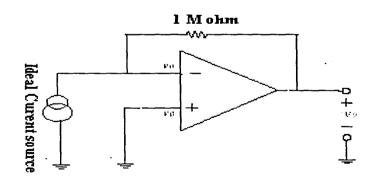

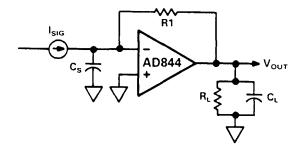

#### Current to voltage converter

Considering the ideal current source (having zero impedance), the fig 2.11 is simple example of current to voltage converter. Few microampere current can be converted into 1-volt output voltage. Since the noninverting input is grounded, the converted inverting input is at virtual ground all the current that produces in ideal current source (considering very high input impedance of op-amp) flows through the external resistor.

#### **Current to voltage converter**

Fig 2.11

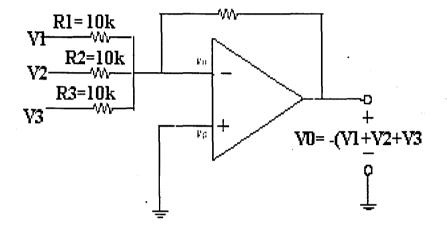

#### Summing amplifier

Fig 2.12. shows a basic summing amplifier. Since noninverting input is grounded, the inverting input is at virtual ground. The current flowing through all the input sources flows through the feedback resistor R4 so

$V_1/R_1 + V_2/R_2 + V_3/R_3 = -V_0/R_4$

If  $R_1 = R_2 = R_3 = R_4$  then  $V_0 = -(V1 + V_2 + V_3)$

Fig 2.12

We have used this summing configuration in the input stage of control amplifier of potentiostat.

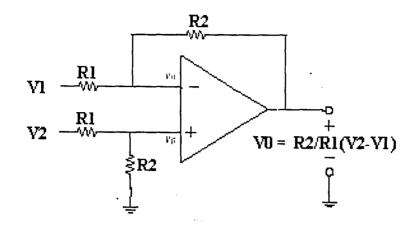

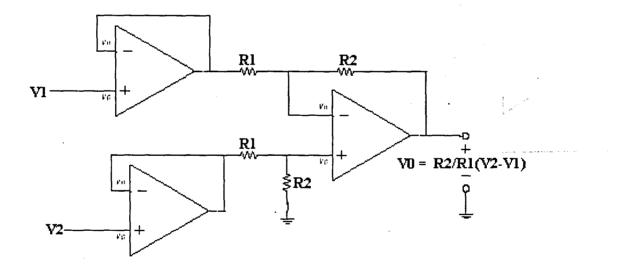

#### Instrumentational amplifier

A differential amplifier has 2 inputs and one or two outputs. Its output reads the difference between two inputs multiplied by some factor, which is determined by external circuitry. Fig 2.13 shows a classic differential amplifier, which has gain R2/R1. It is some times referred as substractor also.

The term instrumentational amplifier is used for a high gain dc-coupled differential amplifier with single ended output, high input impedance and high CMRR. The circuit given in fig. 2.13 also acts as instrumentational amplifier, but its input impedance is relatively low, so to raise the input impedance two buffer voltage followers are used in each input points. This type of configuration is shown in fig 2.14 and called instrumentational amplifier. The output  $V_0 = R_2/R_1$  (V<sub>2</sub>- V<sub>1</sub>). If  $R_2 = R_2$  then the output is just the difference between the two input signals. The disadvantage of this circuit is it requires high CMRR of both followers and also of the difference amplifier. It also requires precise resistor

22

្រំ ១៩១ ១ . ខេត្តស្រំ ៖

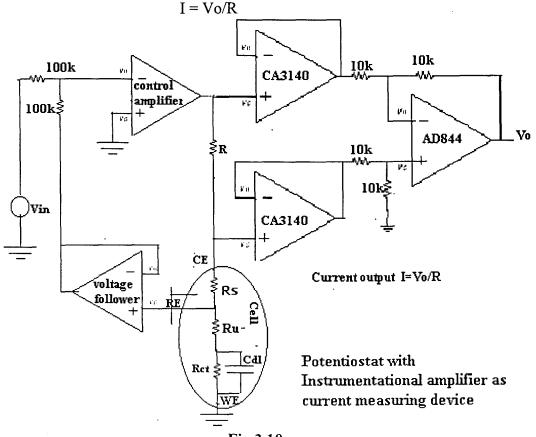

We have used this configuration to measure the current in potentiostat. CA3140 serves as two-voltage follower and AD 844 acts as differential amplifier in our configuration.

### **3 <u>POTENTIOSTATS AND GALVANOSTATS</u>**

A potentiostat is a device, which controls the potential between *working electrode* (WE) and reference *electrode* (RE) at a fixed desired potential. The potential may be programmable varying with time. A minimum three-electrode electrochemical system is desirable for this electrode potential control system. The potential of working electrode, lying in its electrolyte environment, is controlled with respect to Reference electrode (RE)

The reference electrode is designed such that any current that passes through it must not disturb the interfacial potential between RE and solution, such electrode is termed as non-polarisable electrode. Even though modern potentiostats limits such current to very small amount (in the order of pico ampere), proper designation of it is desirable.

A third electrode called counter electrode (CE) is used to supply the current that flows through the cell. Since WE is located in resistive medium, when a current 1. flows through the cell there will be potential gradient around the WE due to iRu drop, where Ru (called as uncompensated resistance) is the solution resistance between WE and RE.

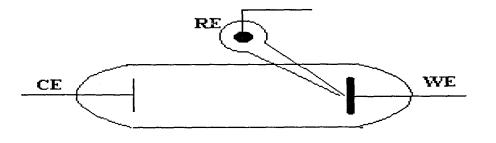

For a physical size of electrode Ru will be pretty large, so a method is adopted to minimise Ru. RE is enclosed in nonconducting envelope having only small hole, which communicates between electrolyte inside and the electrolyte around WE. The vessels tip is kept closed to surface of WE; this configuration used to minimise Ru is called Luggin capillary. In practice Ru can never be zero. Fig 3.1 shows a conventional representation of RE in Luggin capillary.

Conventional representation of reference electrode contained in Luggin Capillary

#### Fig 3.1

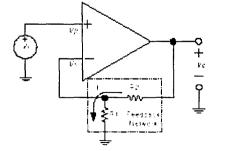

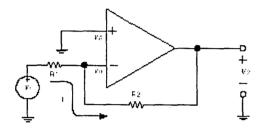

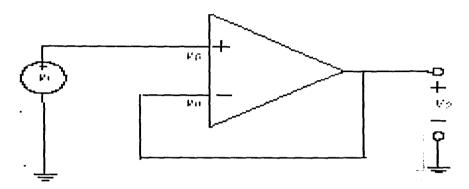

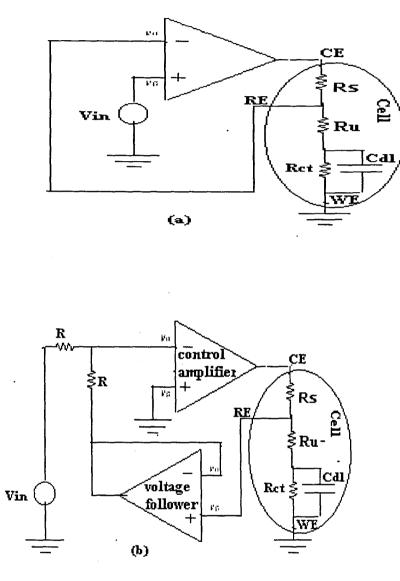

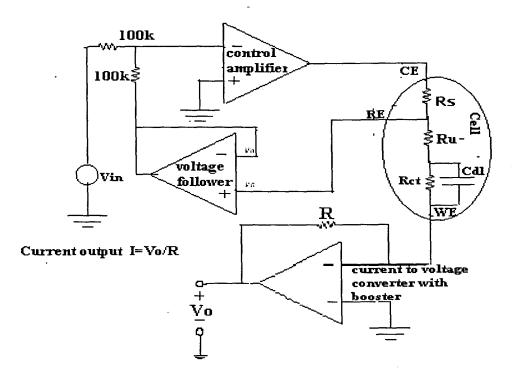

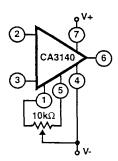

There are several possible configurations for potentiostat: we discuss about some simplest configurations here. Fig 3.2 (a) shows a simple single op-amp potentiostat, in which the control input is given to the noninverting input of the op-amp. Output of op-amp is connected with CE. RE is connected to inverting input of op-amp, which makes a negative feedback path between output and inverting input. WE is grounded. Since

the noninverting input potential Vp = Vin and inverting input potential Vn = Vref. Then by the relation for op-amp inputs Vp = Vn, it can be clearly seen that Vin = Vref.

Fig (a) circuit is of practical use, if current required is very small, and if WE has only resistive impedance, then one can use this circuit to control the potential. The opamp in this case should be some FET (MOSFET) device such as CA3140 which has very small input bias current. If bipolar op-amp like 741, which has input bias current some tenth of nanoamperes, is used for this purpose, then there will be an error of the order of 0.1 V in the WE potential, for  $10^5\Omega$  impedance of RE.

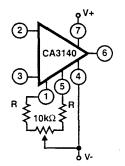

A modification of the circuit (a) is given in (b), in which the problem of bias current is eliminated upto certain level by using FET voltage follower. Here voltage

follower (in our case CA3140) acts as isolator or buffer. It is true that slight complication in frequency response arises due to the addition of voltage follower but it has to be paid for improvement of sensitivity. Another modification in this circuit is the summing configuration in the inverting input. One can apply more than one input simultaneously (Not shown in fig), through a resistor R at the same summing point of inverting input of *control amplifier*.

If  $E_{WR}$  is the potential difference between WE and RE then,  $E_{WR} = E_W - IR_U - E_{ref}$  (3-1)

Since WE is grounded,  $E_W$  is zero here. The output of voltage follower is just  $E_{RW} = -E_{WR} = IR_U + E_{ref}$  (3-2)

In the summing node, which is at virtual ground, of op-amp, using krichoff's law (Sum of total current at a junction is zero)

$$\frac{E_{RW}}{R} + \frac{V_{in}}{R} = 0 \implies -E_{RW} = -(IR_U + E_{ref}) = V_{in} = E_{WR}$$

(3-3)

In this manner the potential  $E_{WR}$  is controlled in this configuration.

Here we have considered the op-amp as ideal one, which has very high gain irrespective of frequency of stimulus. This is not true for all practical potentiostat as well as op-amps. Manufacturers' datasheet only gives the responses in ideal cases. The question of frequency response is quite tedious than that is considered. Since the feedback path in a potentiostat includes the cell itself, the dynamic behaviour of a potentiostat depends upon the type of cell under study at higher frequencies. The theories of dynamic responses are reviewed in detail (voraunhofer and Banks 1972, Harrar and Pomernaki 1973).

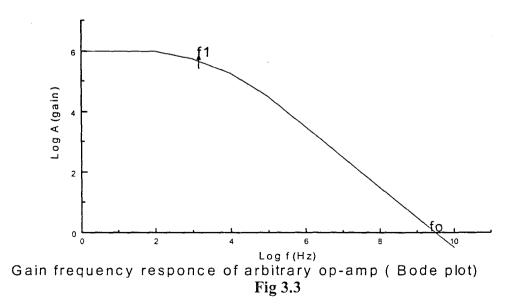

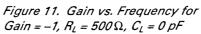

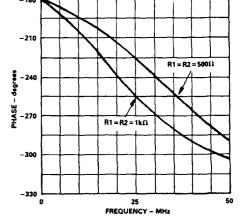

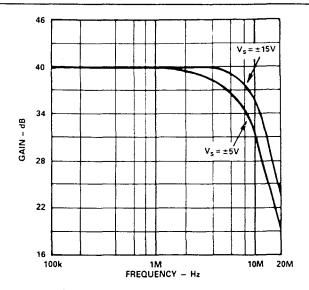

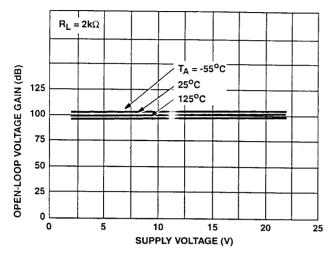

We are going to discuss ,in a crude way, that what factor does in general affect the frequency response of potentiostat. Most op-amps have a frequency response of the type as shown in fig3.3. It is a Bode plot X-axis of which is log of frequency and Y-axis is log of gain. The point F1 is called high frequency turnover point or 3db below point, this is the turning point of the gain versus frequency plot of op-amp. Beyond this frequency F1, the gain decreases by 20db/decade (or in Bode plot by the slop -1). The gain reaches at  $1(\log 1 = 0)$  at the frequency F0, called gainbandwidth product and which is given in datasheet). At further higher frequency the slop changes to -2. Same process occurs in case of phase (For detail with refer to any standard electronics book), The phase difference between input and output reaches almost 90 degree at F1 and remains constant when the gain decreases with -1 slope in Bode plot. At the unity gain frequency F0 the phase difference reaches to 180 degree. Further increase in frequency makes the phase shift more than unity, but this makes the output in same phase with that of inverting input due to 180 degree phase shift. Potentiostat if operated in these high frequencies, easily converted in to oscillator!! due to positive feedback rather than negative

Fig 3.4

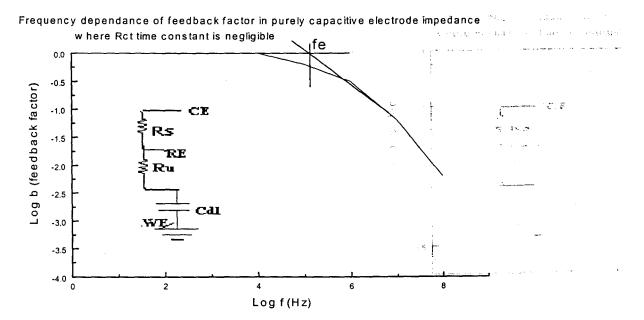

Considering the fig 3.2 (b) and the equivalent circuit of purely capacitive cell (Where Rct = 0 or negligible for high frequency), then feedback factor for negative

feedback becomes,

$$b = \frac{\frac{1}{2\pi f C_{dl}}}{R_s + R_U + \frac{1}{2\pi f C_{dl}}} \qquad \dots (3-4)$$

At frequency  $f_e = \{2\pi (R_U + R_S)C_{dl}\}^{-1}$ , the feedback factor decreases with a slope -1 in Bode plot. If there are significant resistance  $R_{ref}$  in RE lead and capacitance  $C_{ref}$ between RE to WE then the feedback factor again takes turn at the frequency  $f_r = \{2\pi R_{ref}C_{refl}\}^{-1}$  and decreases by negative slop of -2 in the Bode plot (-40db/decade). As the negative feedback factor decreases the gain increases driving the potentiostat towards oscillation. By doing proper cell adjustment this second turning frequency can be made very large. There are various techniques described in literature to minimise such shortcomings ( Ref: Robert Greef, J.physics E Sci.Instrum., Vol. 11, 1978). One must take care of such limitation by proper handling the devices. We will discuss some simple tricks, which will be useful for handling our "home made" devices in later topics.

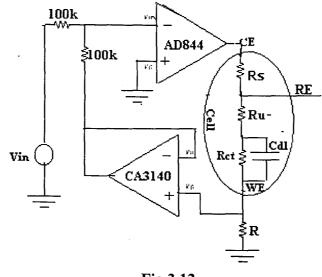

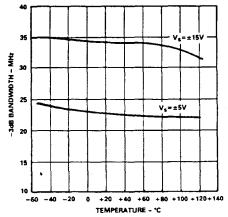

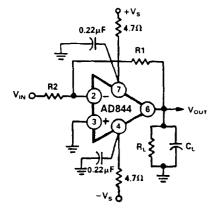

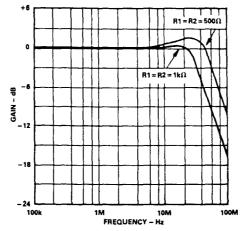

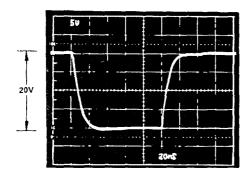

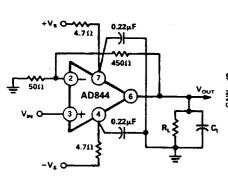

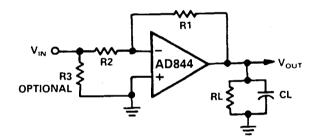

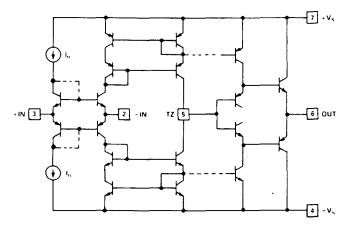

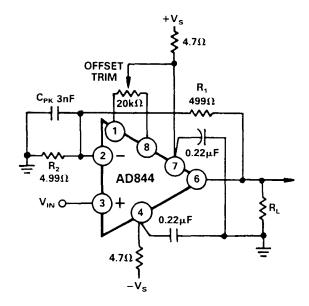

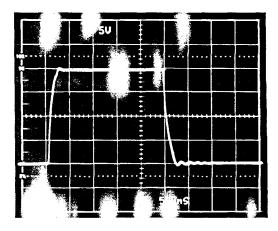

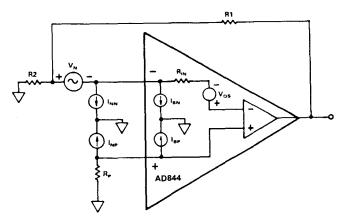

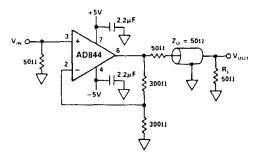

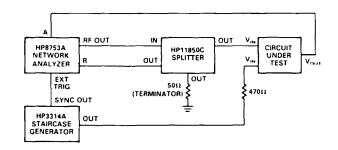

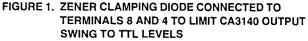

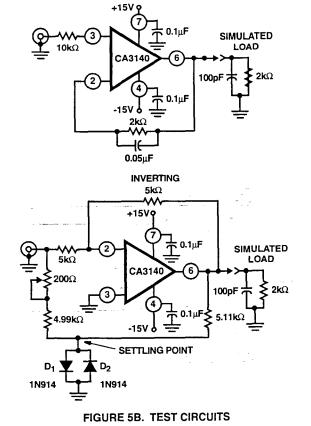

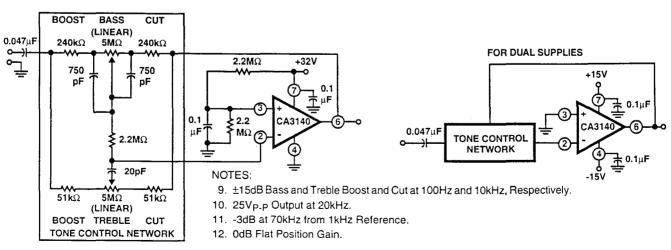

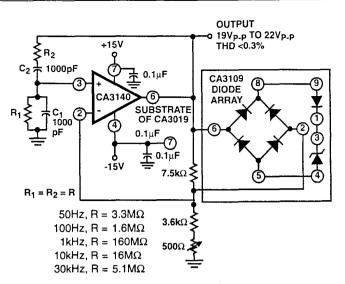

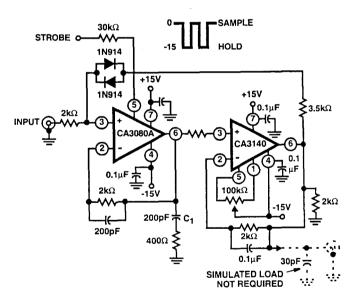

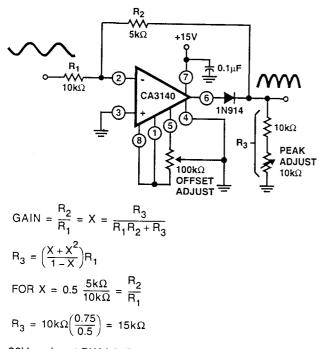

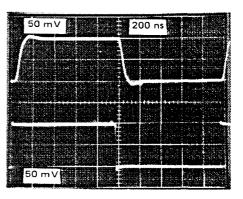

We are basically intended to design a potentiostat which has large bandwidth, which can be operated upto few mega hertz frequency without any distortion, attenuation and phase shift. In our preliminary testing period we used the fig 3.2 (b) type configuration with AD844 as control amplifier and voltage follower since it has large bandwith 60 MHz and high slew rate 2000V/ $\mu$ s. But AD844, which has complementary bipolar junction is not suitable for voltage follower and it draws sufficient amount of current. So we used CA3140 as voltage follower, which is 4.5 MHz, BiMOS op-amp with MOSFET input and Bipolar output and it has slew rate 9V/ $\mu$ s. We used *Stanford Research System DS 340* function generator as signal source (50 $\Omega$  output impedance) and the output is viewed in *oscilloscope(1 M\Omega input impedance)* with different dummy cells.

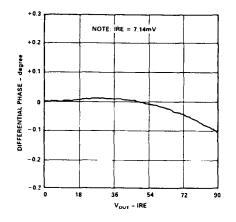

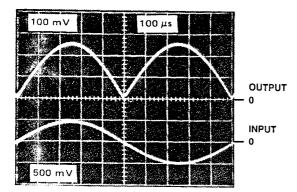

With a dummy cell in which  $Rs = 1.2 k\Omega$  and  $Ru + Rct = 1 k\Omega$  and Cdl = 0 the output (potential at RE) was same as input for a frequency range of 0.1 Hz to 1.2 MHz, when input potential was sine wave of rms value 20 mV. There were 180° phase shift upto 400kHz, upto 1.2 MHz a phase shift of 150° (+30°) appeared in the output.

With another dummy cell where  $Rs=1.2~k\Omega$ ,  $Ru=20\Omega$ ,  $Rct=1~k\Omega$  and  $Cdl=0.1\mu F~$  there were zero phase shift and no attenuation in the RE potential with respect to WE (ground) up to 300kHz .The RE potential was same upto 1.2 MHz but the phase shift was 60° at this potential.

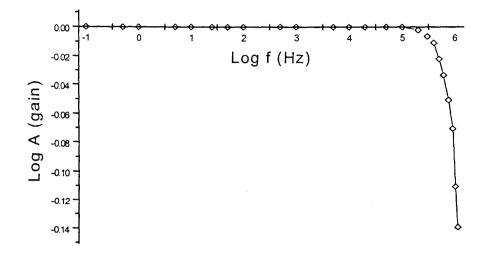

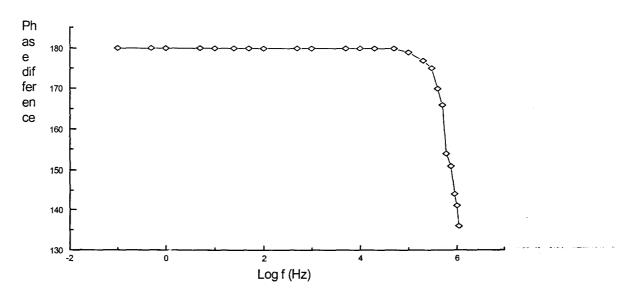

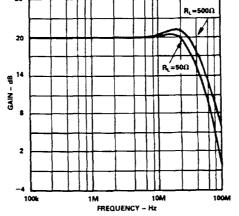

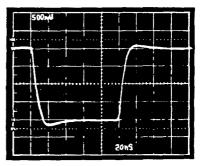

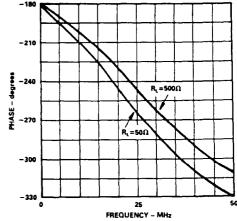

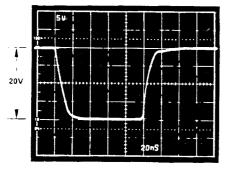

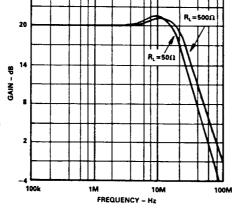

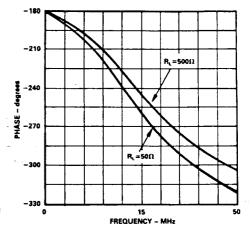

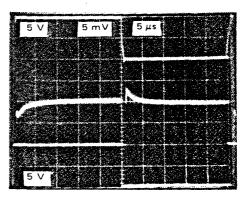

When  $Cdl = 10 \,\mu\text{F}$  and all other circuit remaining same the RE potential was same upto 600 kHz with phase shift 20°. The Bode plot of the gain Vs frequency for this dummy cell is shown in Fig3.5, and the Bode plot of phase Vs frequency is shown in Fig3.6. As compared to commercially available *PAR 263A* potentiostat this result was much satisfactory, since it can operate 1.5 decade more than PRA 263A in the frequency band.

But the configuration has some limitation on its current output, since AD844 can deliver maximum 50mA output current, as specified by the manufacturer. For many experiment in which the current requirement are low it can safely be used but the power booster in the output of control amplifier is desirable for various type of application.

Fig3.5

Bode plot of feedback voltage gain ( RE potential divided by input voltage in dummy cell ) with frequency, when Cdl = 10 microfarad, Rs=1200 ohm, Ru=20 ohm, Rct=1000ohm

Fig3.6

The plot of frequency Vs the phase difference between input and the RE potential of dummy cell when sinusoidal signal of 20mV was applied, in the potentiostatic configuration of Fig 3.2 (b). Dummy cell with Cdl=10microfarad, Ru=20ohm, Rs=1.2kohm and Rct=1kohm

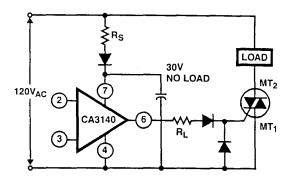

#### **3.1 Current booster**

Some electrochemical applications require high voltage as well as high current. The low power op-amp like AD 844 can't deliver high voltage and current so some sort of boosting of current as well as voltage is required.

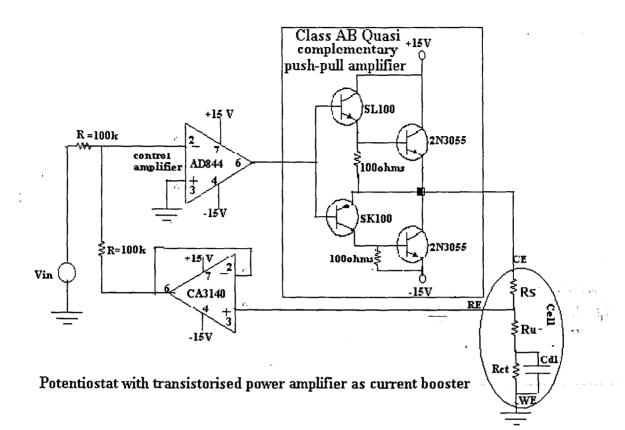

The frequency response of single transistor power amplifier is seriously limited due to the transformer characteristics that require at the output. So two transistor complementary push-pull class AB amplifier, which has low output impedance due to emitter follower configuration, can be used to boost the current. If large current is required one can use quasi-complementary symmetry push-pull configuration, in which 2 moderate power complementary (NPN and PNP) transistors and 2 high power similar (or complementary) transistors are used. Two darlington pairs are formed in this configuration. We used moderate power transistor SL100 and SK100 (Complementary NPN and PNP) and 2 power NPN power transistor 2N3055. Fig 3.7 shows the configuration, which we used for boosting the cell, current

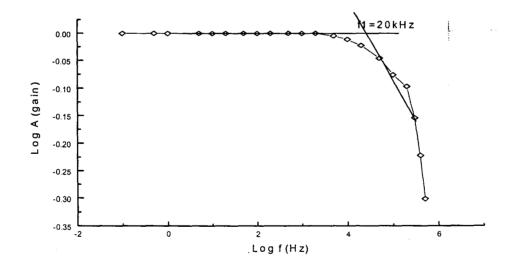

Previous type of dummy cell was used to test the frequency response of the combination, but there was large attenuation at about 20 kHz frequency and 20 mV of input sinusoidal signal. Similarly large phase shift occurred at higher frequency. The Bode plot of the voltage gain Vs frequency is as shown in Fig3.8 (The plot of phase Vs frequency is not shown).

Fig 3.7

Fig 3.8 The Bode plot of the gain( RE potential divided by input potential in the dummy cell as previous) Vs frequency **STUTTERI HORASES MARKAR** .08 - 3POLADMAR SESSION

#### Current booster

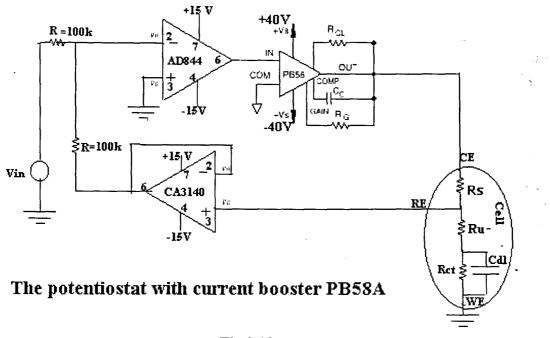

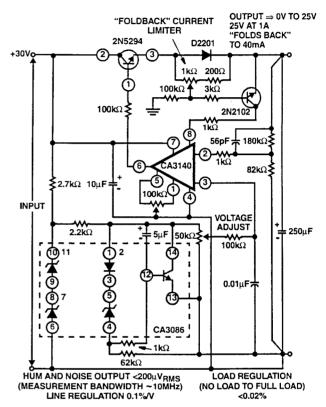

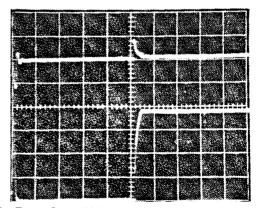

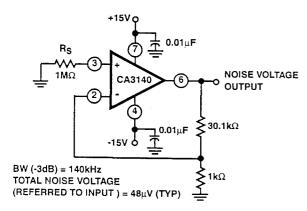

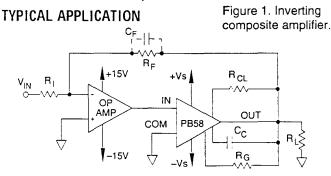

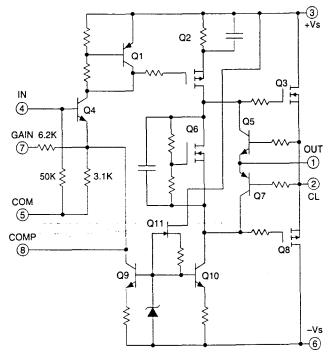

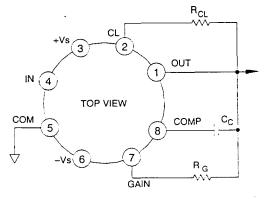

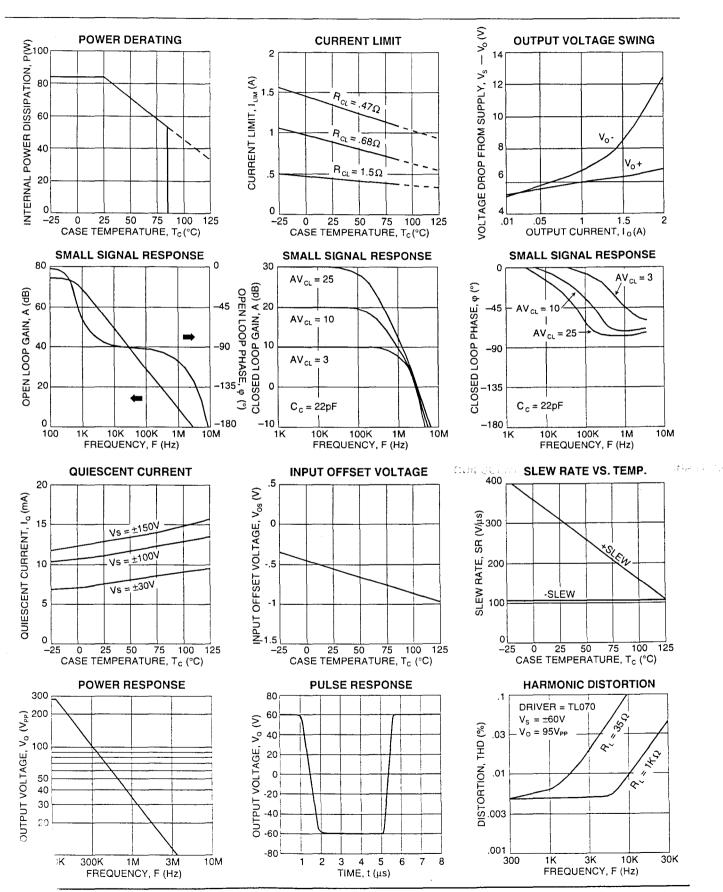

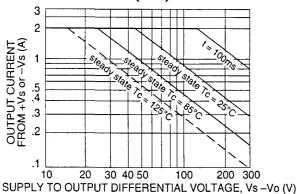

The above configuration has very poor frequency response so we used some high(moderate) frequency high current power op-amp. PB58A is one that we used as current booster. Here are some features of PB58A as given by manufacturer.

| FEATURES                                                                                                             |                  |     |

|----------------------------------------------------------------------------------------------------------------------|------------------|-----|

| WIDE SUPPLY RANGE — $\pm 15V$ to $\pm 150V$                                                                          |                  |     |

| HIGH OUTPUT CURRENT —                                                                                                |                  |     |

| 1.5A Continuous (PB58)                                                                                               |                  |     |

| 2.0A Continuous (PB58A)                                                                                              |                  |     |

| VOLTAGE AND CURRENT GAIN                                                                                             |                  |     |

| HIGH SLEW — 50V/ms Minimum (PB58)                                                                                    | -<br>            |     |

| 75V/ms Minimum (PB58A)                                                                                               |                  |     |

| PROGRAMMABLE OUTPUT CURRENT LIMIT<br>HIGH POWER BANDWIDTH — 320 kHz Minimum                                          | s                |     |

| HIGH POWER BANDWIDTH — 320 kHz Minimum                                                                               | s 1 <u>11</u> 11 |     |

| LOW QUIESCENT CURRENT — 12mA Typical                                                                                 | RREAL            | i . |

| APPLICATIONS                                                                                                         |                  |     |

| HIGH VOLTAGE INSTRUMENTATION                                                                                         |                  | •   |

| Electrostatic TRANSDUCERS & DEFLECTION                                                                               |                  |     |

| HIGH VOLTAGE INSTRUMENTATION<br>Electrostatic TRANSDUCERS & DEFLECTION<br>Programmable Power Supplies Up to 280V p-p |                  |     |

|                                                                                                                      |                  |     |

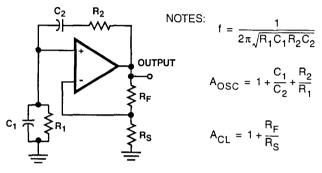

PB58A has small signal bandwidth, with  $\pm 30$  volt power supply, 1 MHz at voltage gain 3. It has also comparatively high slew rate, which is useful figure for our use. PB58A has external current limit resistance R<sub>CL</sub> from pin number 1 to pin number 2, The value of R<sub>CL</sub> is calculated as,

+I<sub>L</sub> =  $0.65/(R_{CL} + 0.01)$ , -I<sub>L</sub> =  $0.65/R_{CL}$ .

Where  $R_{CL}$  is in  $\Omega$  and  $I_L$  is in Ampere. We have limited the load current to 1.3 Ampere by putting  $R_{CL} = 0.5 \Omega$ .

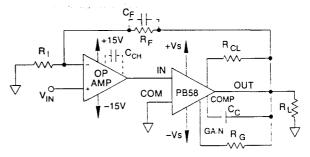

Cascading two amplifiers within a feedback loop has many advantages, but also requires careful consideration of several amplifier and system parameters. The most important of these are gain, stability, slew rate, and output swing of the driver. Operating the booster amplifier in higher gains results in a higher slew rate and lower output swing requirement for the driver, but makes stability more difficult to achieve. For the stability, the gain of the booster is fixed to minimum value and the driver (control amplifier in our case) is free to control overall gain. The slew rate of the closed loop is the booster gain times the slew rate of control amplifier maximum upto slew rate of booster. Here control amplifier AD844 has very high slew rate 2000 V/ $\mu$ s so overall slew rate is theoretically equal to the slew rate of booster 75 V/  $\mu$ s. The slew rate decreases by minimising the booster gain but this is to be paid for the stability.

#### Current booster

The phase shift inside the closed loop is minimised by using a compensation capacitor Cc between the pin 1 to 8 in PB58A. This value is given in datasheet, we have used 10pf for this purpose.

The gain of booster is set by using an external resistance  $R_G$  between pin number 7 to 1 by the following relation. (Given by datasheet, which can be realised by studding the internal equivalent circuit, see datasheet of PB58A)

$R_{G} = \left[ \left( A_{V} - 1 \right) 3.1 k\Omega \right] - 6.2 k\Omega$ or,  $A_{V} = \frac{R_{G} + 6.2 k\Omega}{3.1 k\Omega} + 1$

Where  $A_V$  is the gain of booster.  $R_G$  is kept equal to zero in our configuration for stability so that the gain of booster remains minimum(=3).

#### Fig 2.10

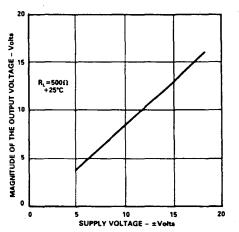

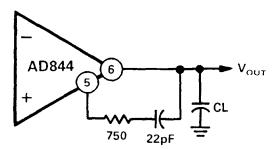

The power booster is inserted in the loop of the control amplifier and cell through voltage follower forming a closed negative feedback loop as shown in Fig 2.10. Since the control amplifier supply voltage is  $\pm 15$  volts, the control amplifier output can oscillate upto  $\pm 11V$  (see data sheet). The power booster has constant gain of 3 so for it to oscillate it requires more than 35 Volts. Even though the booster works at  $\pm 15$  V, to avoid the saturation  $\pm 40$  V supply is given to it. The whole PB58A power op-amp is mounted in a proper heat sink. For small value of Cdl (Not purely capacitive cell in Electrochemist's terminology) it can control the potential upto 1 MHz !! within 10% error and about 30 degree phase shift.

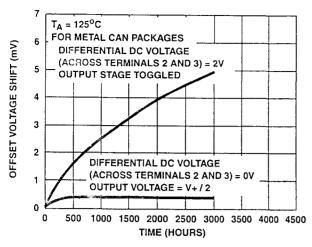

The dc performance of the potentiostat is another measure of accuracy. The voltage follower CA3140 has maximum dc error of 5 mV. This figure is pretty large, but it can be minimised by using the null offset option (see the datasheet).

### 3.2 Measurement of Cell Current

Cell current measurement requires another important consideration. Since the whole cell is 'inside' the loop of the feedback to control amplifier, one cannot insert any mechanical or passive current measuring instrument in the loop. If one does so the whole circuitry will be disturbed and can't get required result within certain limit of accuracy. Direct current measuring is rather difficult and not accurate method. Many current measuring instruments actually measure voltage that is produced across a known resistor when the current flows through that resistor. There are basically two methods of measuring current in a cell, which are discussed in many literatures and followed by the electrochemist and the instrument manufacturers.

1) Using Instrumentational amplifier.

2) Using current to voltage converter.

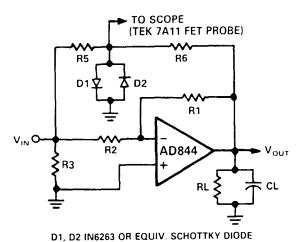

### 1) Cell current measurement by instrumentational amplifier

As already mentioned the three op-amps configuration (Two CA3140 and one AD844) as shown in fig 3.10 forms so called instrumentational amplifier. It measures the difference between two inputs. Here all the resistances are equal (10k  $\pm$ 1%) so the gain of the instrumentational amplifier is 1. It draws negligible amount of current from the cell current path . A resistance of known value R is inserted between the booster output (not shown in fig) and the counter electrode and across it the two inputs of instrumentational amplifier is connected. If Vo is the voltage read at the output of Instrumentational amplifier due to a flow of current I in the cell then,

Fig 3.10

### Potentiostat

Thus the current is read in this configuration. The main advantage of this configuration is that another power booster is not required for the measurement of current as in current to voltage converter and also low power op-amps which are used here are less or more free from the bandwidth and slew rate limitations.

### 2) Cell current measurement by current to voltage converter

In this configuration, as shown in fig 3.11, the working electrode is connected with the inverting input of the current to voltage converter with booster (Because the same amount of current that is given by the control amplifier booster must supply by the output of the converter). Since the noninverting input of the converter is grounded, the WE is at virtual ground and rest processes are same. A known resistance R is connected between the output of current to voltage converter to its inverting input. The whole current that flows through the cell is supplied through R so an inverted output voltage is set in the converter's output. If 'I' is the current flowing through the cell and Vo is output voltage then current through the cell is,

$$I = Vo/R$$

Fig 3.11

The main advantage of this configuration is that the feedback loop, which the cell forms, remains unaffected. But we prefer the instrumentational amplifier to measure the current not because the second method is worst but because of our slew rate and the high frequency requirement. Since we have used AD844 as the control amplifier here also for

## Potentiostat

the same reason Ad844 has to be used but AD844 has very small (50 ohm) inverting input resistance. So AD844 can't be used as converter.

## <u>Compensation of uncompensated resistance Ru</u>

Since there are always some resistance between RE and the electrolyte surrounding of WE called RU, uncompensated resistance, which always wrong value of WE potential by an amount I  $R_U$  when a current I flows through the cell. There are many techniques described in literatures to decrease it. By electronic configuration the voltage drop across it can be compensated just by giving a positive feedback to the control amplifier. The positive is given through a potentiometer. A potentiometer of 10k and 10 turn can be applied for this purpose. One edge of potentiometer is grounded and another end is connected with the current output. The sliding end of potentiometer is connected to the inverting input of the control amplifier. Since current output is in phase with the input the input signal, the feedback will be positive feedback. If RU is known then a fraction  $R_U/R$  of current output can be fed back to compensate it where R is resistance across the two input of unity gain instrumentational amplifier measuring current.

If RU is not known then there is no hard and fast rule for the compensation (see ref.) and the positive feedback is increased below a point at which the potentiostat just start to oscillate.

\*\*\*

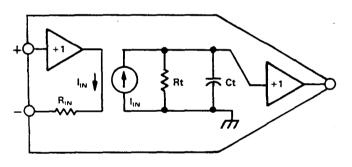

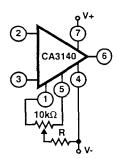

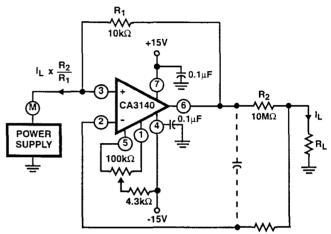

# 3.3 Galvanostat

A galvanostat maintains constant current through the cell by the use of feedback circuitry. Whatever the change in cell impedance the galvanostat must maintain the same current. A simple galvanostat circuit is shown in fig 3.1

Fig 3.12

Fig 3.12 is like a potentiostatic circuit, only the difference here is that, the WE is connected with ground through an external resistance R and the feedback voltage follower is connected with WE in place of RE. If input potential Vin then the voltage follower input must be equal to Vin. If I is current flowing through the cell then,

$$I = \frac{V_{in}}{R}$$

By changing the value of R one can easily set the required value. A potentiostat can thus easily converted into galvanostat so we are not discussing the galvanostat in detail. Our potentiostat can operate in both modes. When the instrument is set to galvanostatic mode WE is connected to voltage follower and the instrumentational amplifier is connected across RE and WE. Similarly the current output in potentiostatic mode becomes potential output (potential between RE and WE) and the potential output in potentiostatic mode, but this flip is done internally so one can read current and potential as it is .

\*

37

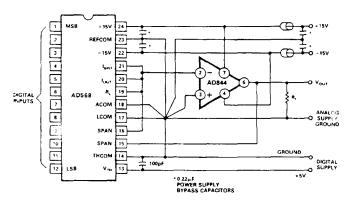

# 4.Design

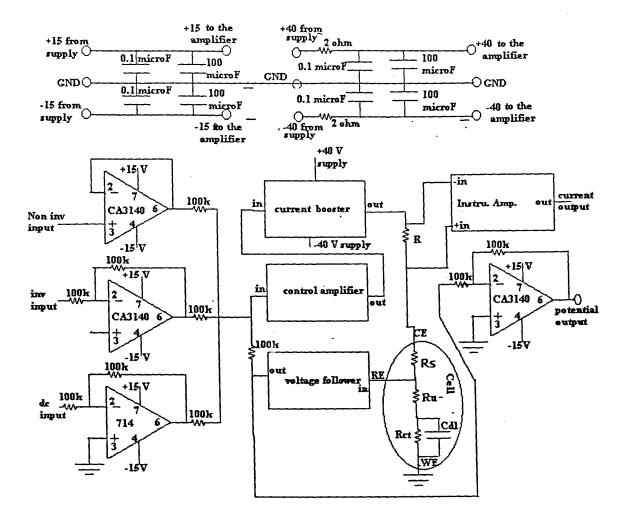

# 4.1 Design and Fabrication

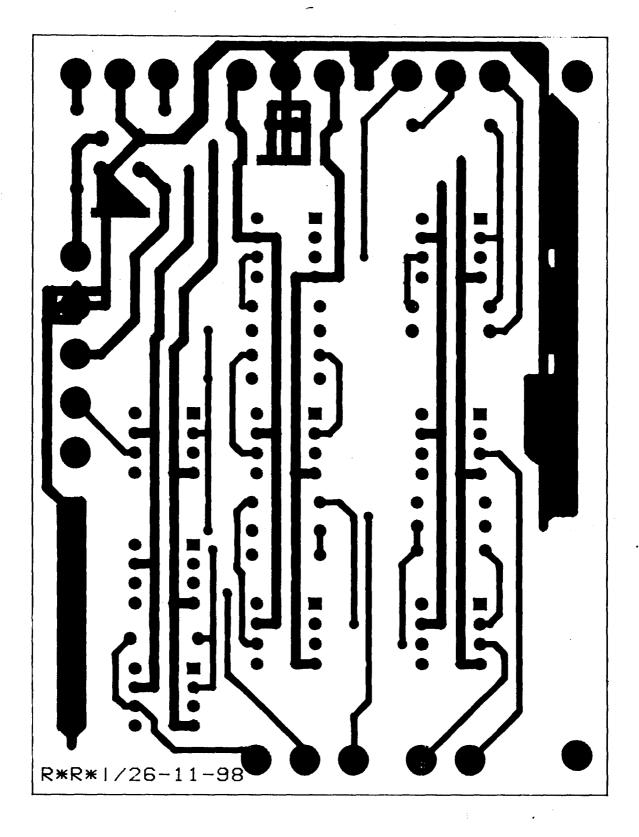

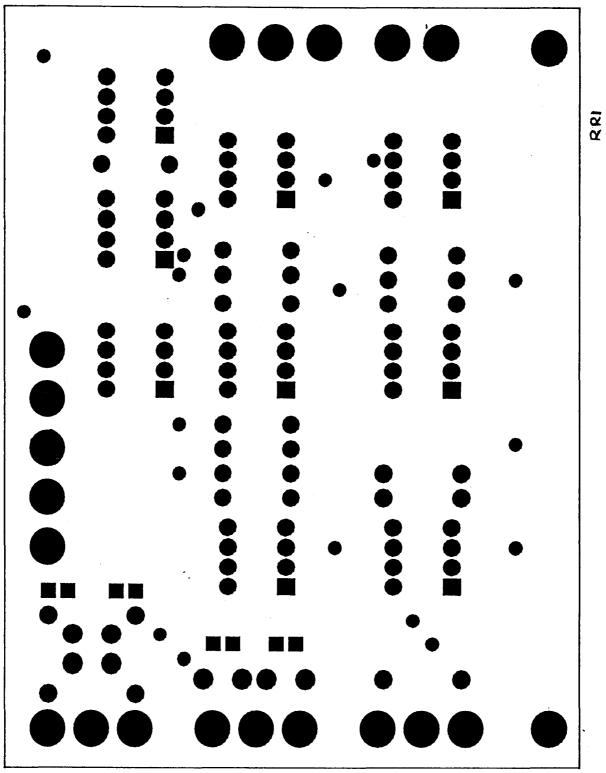

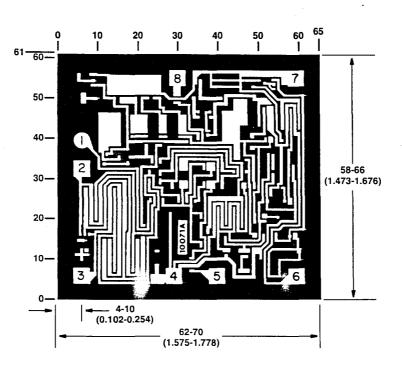

The instrument has been designed to operate for both potentiostatic and galvanostatic mode. The main circuit diagram is as shown in fig 4.1. All the values of the resistors and capacitors are as already mentioned. The printed circuit board (PCB) was designed using ORCAD PCB II software. The layout of PCB is given in Appendix 1.

To control the output current a current limiting resistance is connected between control output to the counter electrode (CE). There are two different resistors, which can be changed by using 2 pole-2 ways rotary switch marked as current range. At 'HI' mode there is 2 ohms resistor and at 'LO' mode there is 1000 ohms resistor.

To measure the current in the potentiostatic mode a resistor is connected between current range resistor to the counter electrode. The resistor is mounted in 5 ways-2 poles rotary switch, marked as 'current sensitivity'. The instrumentational amplifier inputs are connected across this resistor. The output of instrumentational amplifier directly reads the current in mA (in the potentiostatic mode) multiplied by the current sensitivity.

The resistances across the two inputs of instrumentational amplifier and the output current sensitivity multiplication factors have the following relations :

| Current sensitivity | Resistances |  |

|---------------------|-------------|--|

| ×100                | 10 Ω        |  |

| ×10                 | 100 Ω       |  |

| ×1                  | 1000 Ω      |  |

| ×0.1                | 10000 Ω     |  |

| ×.0.01              | 100000 Ω    |  |

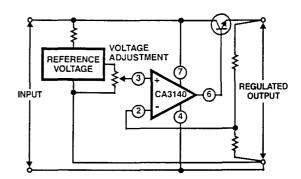

This instrument has its own power supply. A 30-0-30 Volts (100-mA) transformer has been used for main power supply to the instrument. By rectifying it , 1000  $\mu$ F capacitors have been used to filter. It produces 42 Volts unregulated dc voltage. This 42-0-42 Volts dc supply has been given to the current booster. By the same 42-0-42 Volts dc supply 15-0-15 Volts dc has been regulated using 7815 and 7915 regulator ICs. This 15-0-15 Volts supply has been given to the rest of the op-amps.

The whole instrument has been fitted in a  $15 \times 10 \times 8$ ' aluminium box. Two LED DPMs (Digital Panel Meter) of 2 Volts range have been mounted in the front panel of the instrument. One reads dc current and another reads dc potential output. The power supply for the panel meter is separate. This is supplied by another transformer and 5 Volts regulator (7805 IC).

**r**--

38

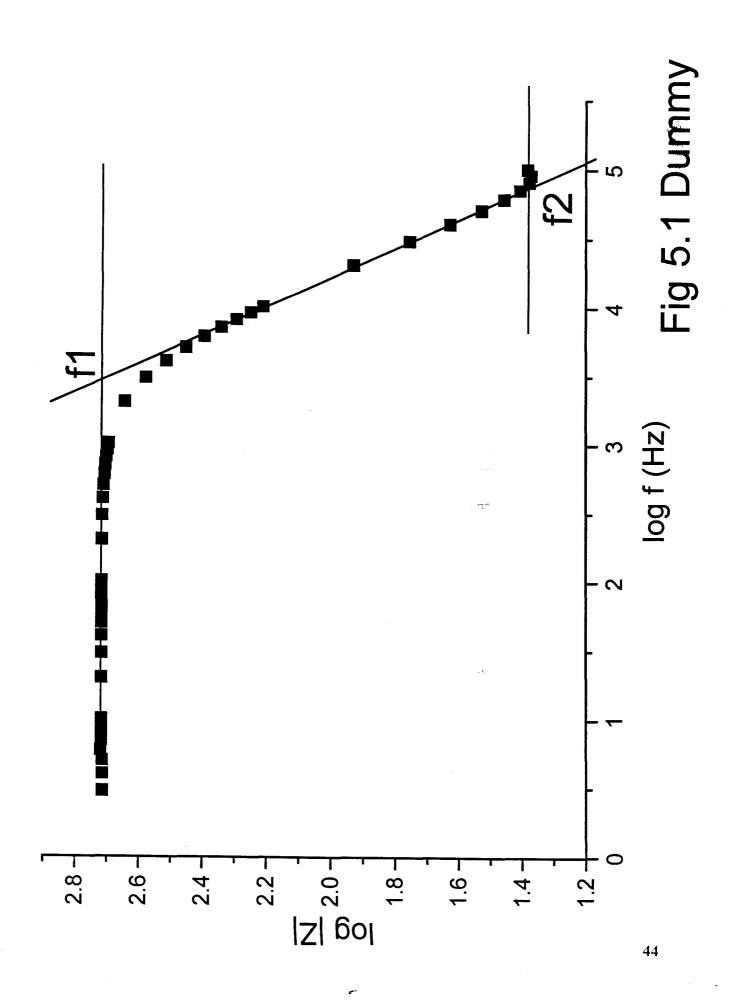

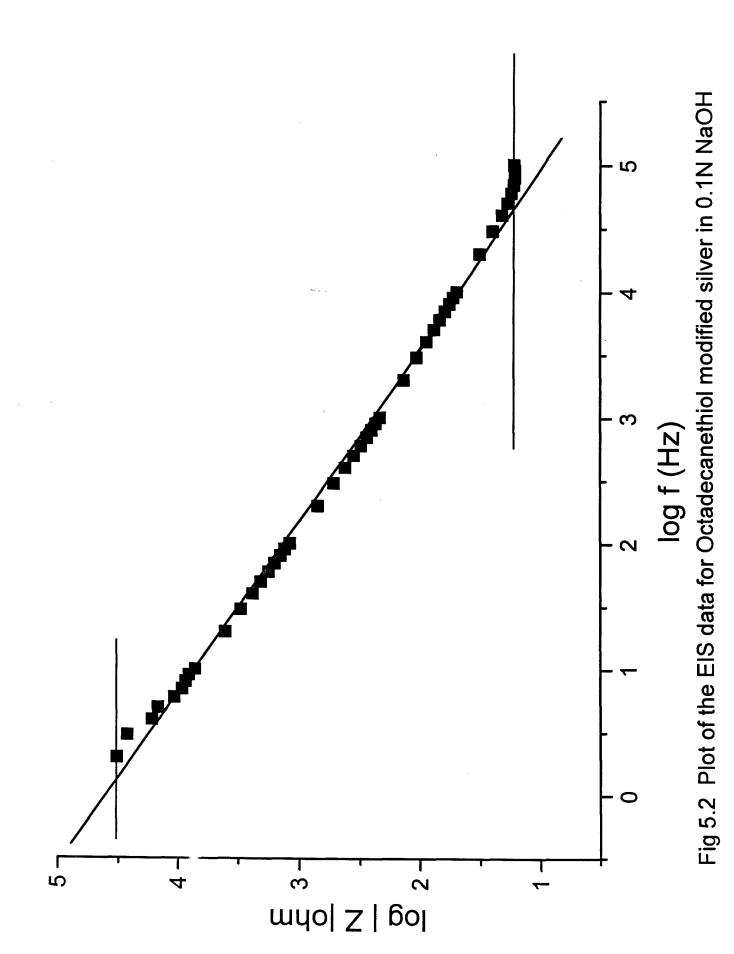

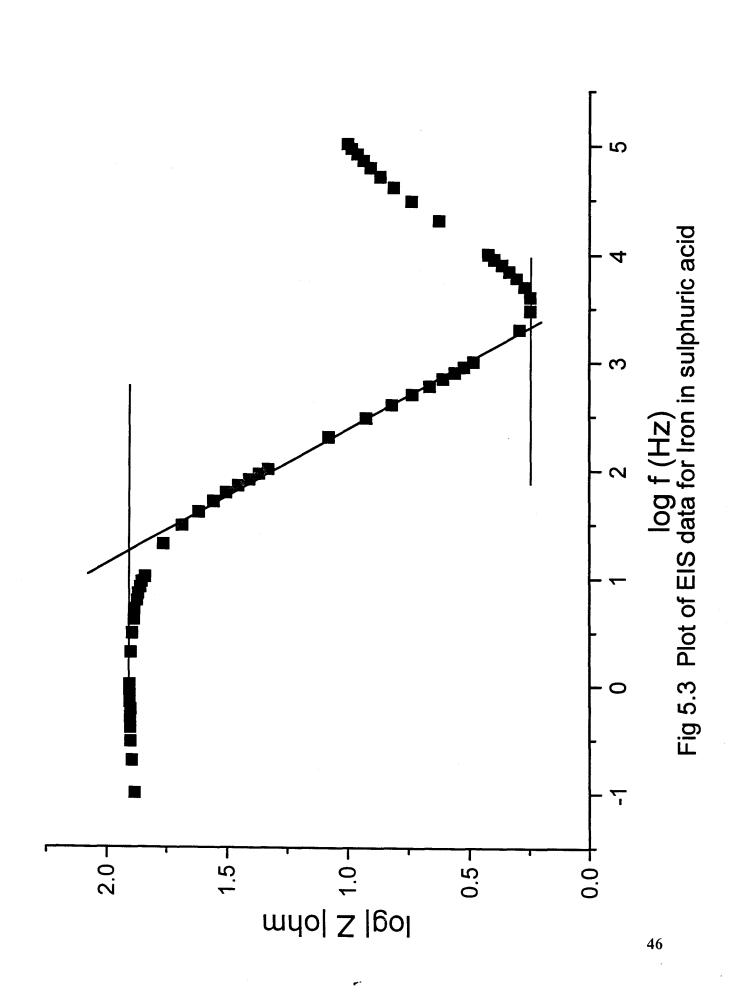

### Design